## **AN11152**

# Reducing the Spurs at RF\_out caused by the biasing choke during fast switching on and off in TDD system

Rev. 1.0 — 20 January 2012

Application note

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | BGA7210, VGA, TDD, Fast Switch, Spurs, OM7921/BGA7210 Customer Evaluation Kit                                                                                                                                                                                                                                         |

| Abstract | The document provides guidelines to reduce the spurs at RF_out caused by the RF_out stage biasing choke during fast switching OFF the BGA7210.                                                                                                                                                                        |

| Summary  | The BGA7210 Variable Gain Amplifier with a fast power on/off mode which can be also used in Base station TX-lines using the TDD (time division duplex) operation systems. The BGA7210 RF output stage uses an external biasing choke. During fast switching off the device, the choke induces spurs at the RF-output. |

|          | This document describes how to reduce the spurs caused by fast switching off the device and the voltage at the inductor.                                                                                                                                                                                              |

**BGA7210**

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 1.0 | 20120120 | Initial document |

## **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### 1. Introduction

This document describes how to reduce the spurs at RF\_out caused by fast switching off (on) the device when this option is used in TDD operation systems. Measurements shown compare the performance using the original external component list (without the shunt capacitor Csh = 0.68 pF) with a tailored component list, which improves the switching behavior at 2.14 GHz.

The BGA7210 MMIC is an extremely linear Variable Gain Amplifier (VGA), operating from 0.7 GHz to 2.75 GHz. The maximum gain is 30 dB. It has an attenuation range of 31.5 dB. At its minimum attenuation setting it has a maximum power output of 21 dBm, an IP30 of 39 dBm and a noise figure of 6.5 dB.

The BGA7210 has been designed and qualified for the severe mission profile of cellular base stations, but its outstanding RF performance and digital SPI interfacing flexibility make it suitable for a wide variety of applications.

## 2. Spurs at RF\_out and their root cause

Spurs occurs at RF\_out during switching off the BGA7210. The root cause is the fast switching of the final stage of the BGA7210 for different reasons, like power saving or to have higher isolation between the RFin and RFout.

The final stage of the BGA7210 is biased by an external inductor which is also in the supply loop. As known, by fast switching off the current through an inductor, the magnetic field will induce a counter electromagnetic force which generates a voltage (spurs).

Vspur = L \* di/dt

The induced voltage (Vspur) peak value and duration is dependent on the fall time of the switch off signal, inductor value, voltage, current through the inductor and the load resistance.

## 3. Options to reduce the spurs at RF-out

The only way to reduce the spurs is to lower the biasing inductor value L2, but that would impact the RF performance, and the matching and the insertion loss would become worse.

Of course the inductor can be damped by series resistor, but this has much more disadvantages than reducing the inductor value.

The induced voltage has two impacts on the circuit:

**BGA7210**

- Induced voltage could damage the final amplifier stage, this case is investigated (simulation and measured), and found that the BGA7210 Breakdown voltage is much higher than the measured/simulated spur voltages.

- 2. Induced voltage generates broadband spurs at the RF-out which can give EMI problems.

To reduce the spurs at RF-out a High pass filter can be used.

There are different HP-filters (Chebyshev, Butterworth, Bessel,...) and types with minimum number of capacitors or inductors.

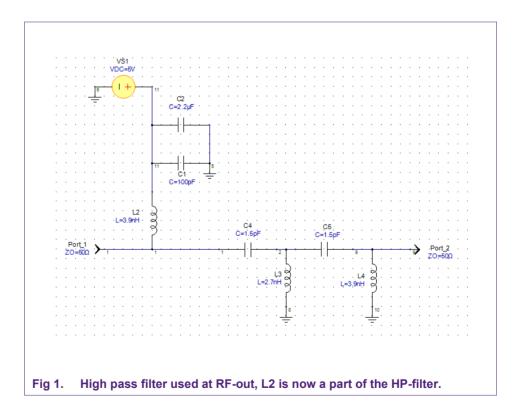

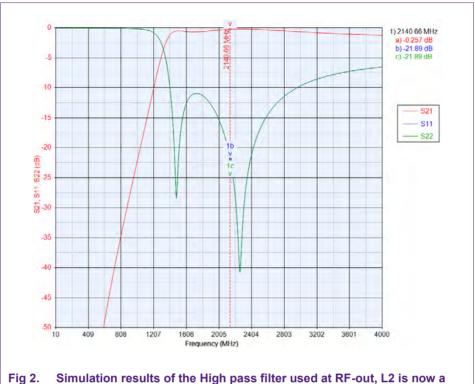

The Chebyshev filter topology has been selected, because it has high attenuation at the stop band, low slope, and matching can be tuned, and requires a minimum value for the inductors. The choke acts as a first inductor (3.9 nH) in this filter topology and has a low inductance. This will induce less spurs than the original 22 nH biasing inductor (L2).

#### Solving the EMI problem using HP-filter will also reduce the induced spur voltage!

Fig 2. Simulation results of the High pass filter used at RF-out, L2 is now a part of the HP-filter.

## 3.1 S-par and linearity measurements original versus HP-filter

Table 1. Linearity results

Measured at 2140 MHz

| Symbol  | Original | With HP-filter |

|---------|----------|----------------|

| PL(1dB) | 20 dBm   | 22.5 dBm       |

| IP3o    | 34 dBm   | 34 dBm         |

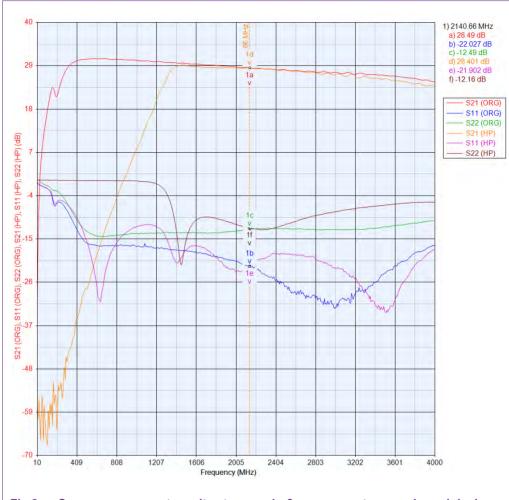

Adding the HP-filter improves the PL(1dB), this can be explained by changing the output matching means improving the matching at the BGA7210 output pin.

Fig 3. S-par measurement results at max gain & max current comparing original components vs. high pass filter used at RF-out, L2 is now a part of the HP-filter.

## 3.2 Measurements on the Spurs at RF\_out using the original components and the proposed HP filter schematic

Spurs are measured with the original components and with the HP-filter which reduce the spurs.

**BGA7210**

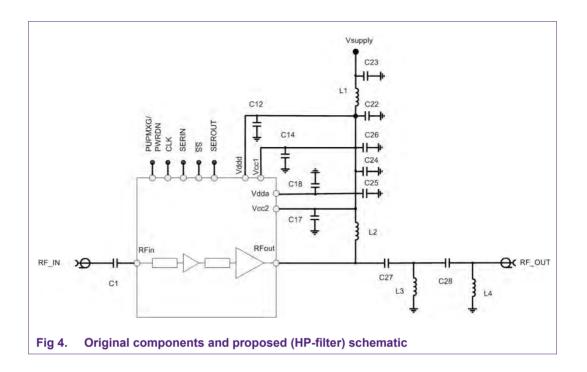

### 3.2.1 Schematic and component list

Table 2. List of components proposed in the BGA7210 Data sheet and with the HP-filter

| Component | Description                     | Value orginal | Value HP-filter | Remarks                        |

|-----------|---------------------------------|---------------|-----------------|--------------------------------|

| C1        | DC blocking capacitor           | 100 pF        | 100 pF          | Murata GRM                     |

| C27       | DC blocking capacitor/HP-filter | 100 pF        | 1.5 pF          | Murata GRM                     |

| C12       | Decoupling capacitor            | 100 nF        | 100 nF          | Close to pin 19                |

| C14       | Decoupling capacitor            | 100 nF        | 100 nF          | Close to pin 17                |

| C17       | Decoupling capacitor            | 100 nF        | 100 nF          | Close to pin 15                |

| C18       | Decoupling capacitor            | 100 nF        | 100 nF          | Close to pin 16                |

| C22       | Optional decoupling capacitor   | 10 μF         | 10 μF           | Part of optional ripple filter |

| C23       | Optional decoupling capacitor   | 10 μF         | 10 μF           | Part of optional ripple filter |

| C24       | Decoupling capacitor            | 100 pF        | 100 pF          | Close to L2                    |

| C25       | Decoupling capacitor            | 100 nF        | 100 nF          | Close to L2                    |

| C26       | Decoupling capacitor            | 4.7 µF        | 4.7 µF          | Close to L2                    |

| C28       | Jumper / HP-filter              | 0 Ω           | 1.5 pF          | Murata GRM                     |

| L1        | Optional inductor               | 820 nH        | 820 nH          | Part of optional ripple filter |

| В | BG/ | ٩7 | 21 | lC |

|---|-----|----|----|----|

|   |     |    |    |    |

| Component | Description                                | Value orginal | Value HP-filter | Remarks                          |

|-----------|--------------------------------------------|---------------|-----------------|----------------------------------|

| L2        | Inductor (biasing final stage) / HP-filter | 22 nH         | 3.9 nH          | Murata LQW 18 (close to RF-line) |

| L3        | HP-filter                                  | n.c.          | 2.7 nH          | Murata LQW 18 (close to RF-line) |

| L4        | HP-filter                                  | n.c.          | 3.9 nH          | Murata LQW 18 (close to RF-line) |

#### 3.2.2 Spur Measurements

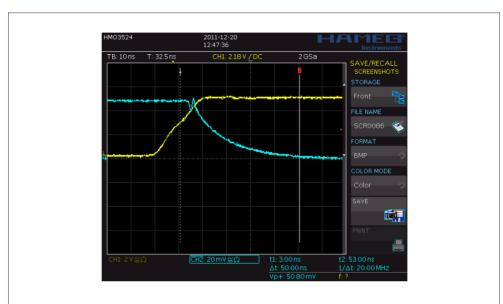

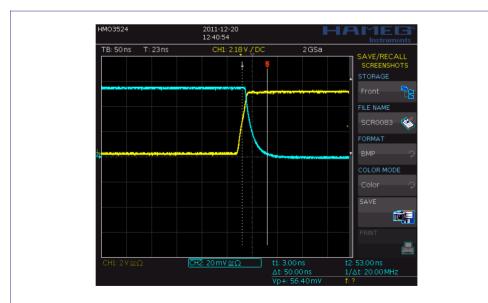

This paragraph plots the spurs at RF-Out in time- and frequency-domain by switching BGA7210 on and off at max current and max gain setting. The switch on/off frequency at PUP-pin is set to 250 Hz, the input and output is terminated with 50 ohm.

#### 3.2.2.1 Spurs in time domain

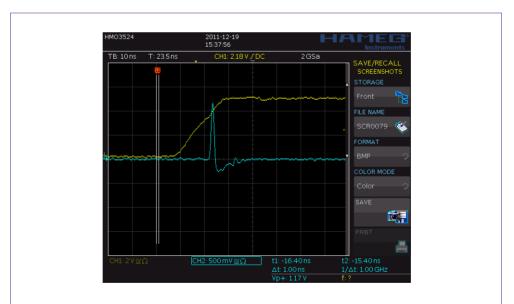

Fig 5. Original: Spur (blue 1.17Vp) at RFout (application board) during switch off sequence (yellow line is switch off signal)

**BGA7210**

Fig 6. Original: Spur (blue 1.07Vp) at BGA7210 RFout pin during switch off sequence (yellow line is switch off signal)

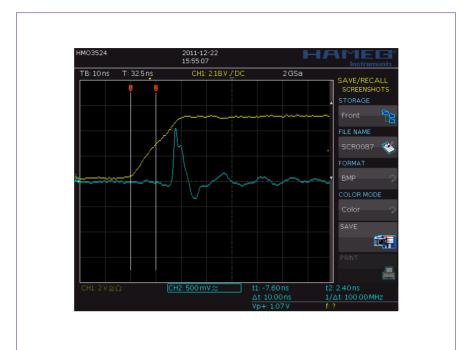

Fig 7. HP-filter: Spur (blue 0V) at RFout (application board) during the switch off sequence (yellow line is switch off signal)

**BGA7210**

Fig 8. HP-filter: Spur (blue 0.29Vp) at BGA7210 RFout pin during switch off sequence (yellow line is switch off signal)

**BGA7210**

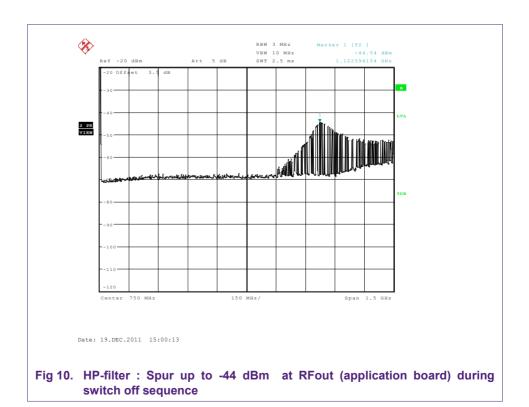

#### 3.2.2.2 Spurs in frequency domain

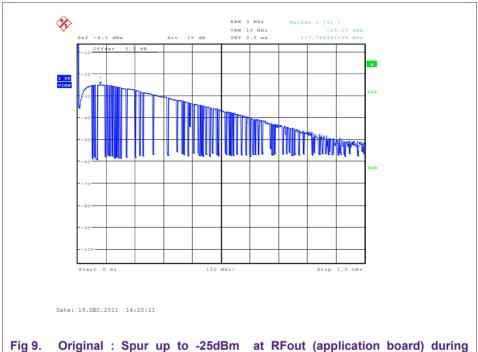

Fig 9. Original: Spur up to -25dBm at RFout (application board) during switch off sequence

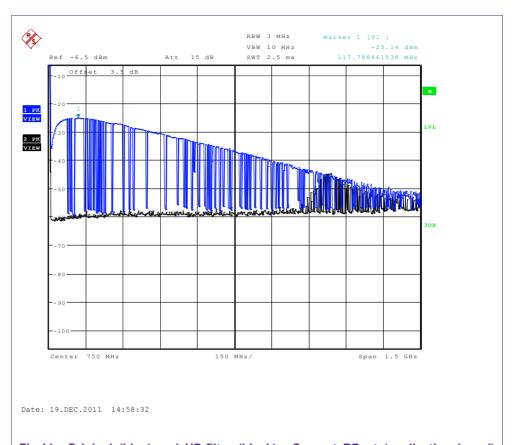

Fig 11. Original (blue) and HP-filter (black) : Spur at RFout (application board) during switch off sequence

12 of 17

#### **BGA7210**

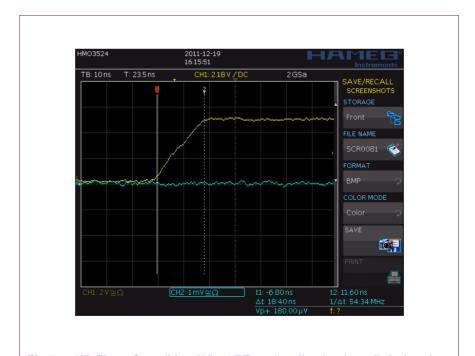

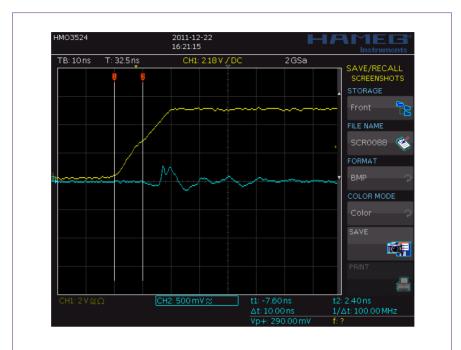

#### 3.2.3 Spurs in Time domain at -20dBm at RFin

This paragraph plots the spurs at RF-Out in time- domain by switching BGA7210 off at max current and max gain setting. The PUP-pin is triggered with 250 Hz, the RF input is set to -20dBm and the output signal is 8.5 dBm measured with a 50 ohm RF-detector.

Fig 12. Original: Spur (blue) at RFout (application board) during switch off sequence (yellow line is switch off signal)

Fig 13. HP-filter: No Spur (blue) at RFout (application board) visible during switch off sequence (yellow line is switch off signal)

## 4. Picture proposed EVB (include HP-filter)

Fig 14. Picture printed circuit board of the BGA7210 with the HP-filter at the RFout.

NXP Semiconductors AN11152

BGA7210

## 5. Conclusion

Changing the biasing of the BGA7210 final stage (adding HP-filter) will improve the P1dB and reduce the spurs at RFout (both at VGA RF-out pin and after the HP-filter).

Other parameters like Spar and OIP3 will be not affected at 2 GHz.

The HP-filter in this App-Note is optimized for frequencies between 1.5 GHz and 2.5 GHz.

In case of using other frequencies the HP-filter should be adapted for your own requirements.

**BGA7210**

## 6. Legal information

#### 6.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 6.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or

customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 6.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

**AN11152 NXP Semiconductors**

#### **BGA7210**

## **Contents**

| 1.      | Introduction                                                                                | 3     |

|---------|---------------------------------------------------------------------------------------------|-------|

| 2.      | Spurs at RF_out and their root cause                                                        | 3     |

| 3.      | Options to reduce the spurs at RF-out                                                       | 3     |

| 3.1     | S-par and linearity measurements original ve HP-filter                                      | rsus  |

| 3.2     | Measurements on the Spurs at RF_out using original components and the proposed HP schematic | filte |

| 3.2.1   | Schematic and component list                                                                | 7     |

| 3.2.2   | Spur Measurements                                                                           | 8     |

| 3.2.2.1 | Spurs in time domain                                                                        | 8     |

| 3.2.2.2 | Spurs in frequency domain                                                                   | 11    |

| 3.2.3   | Spurs in Time domain at -20dBm at RFin                                                      | 13    |

| 4.      | Picture proposed EVB (include HP-filter)                                                    | 14    |

| 5.      | Conclusion                                                                                  | 15    |

| 6.      | Legal information                                                                           | 16    |

| 6.1     | Definitions                                                                                 | 16    |

| 6.2     | Disclaimers                                                                                 |       |

| 6.3     | Trademarks                                                                                  |       |

| 7.      | Contents                                                                                    | 17    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.