### Dual Per-Pin Parametric Measurement Units

### **General Description**

The MAX9951/MAX9952 dual parametric measurement units (PMUs) feature a small package size, wide force and measurement range, and high accuracy, making the devices ideal for automatic test equipment (ATE) and other instrumentation that requires a PMU per pin or per site.

The MAX9951/MAX9952 force or measure voltages in the -2V to +7V through -7V to +13V ranges, dependent upon the supply voltage (V<sub>CC</sub> and V<sub>EE</sub>). The devices handle supply voltages of up to +30V (V<sub>CC</sub> to V<sub>EE</sub>) and a 20V device-under-test (DUT) voltage swing at full current. The MAX9951/MAX9952 also force or measure currents up to  $\pm 64$ mA with a lowest full-scale range of  $\pm 2\mu$ A. Integrated support circuitry facilitates use of an external buffer amplifier for current ranges greater than  $\pm 64$ mA.

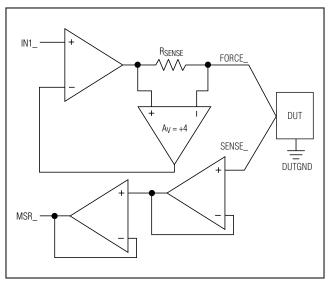

A voltage proportional to the measured output voltage or current is provided at the MSR\_ output. Integrated comparators, with externally set voltage thresholds, provide detection for both voltage and current levels. The MSR\_ and comparator outputs can be placed in a high-impedance state. Separate FORCE and SENSE connections are short-circuit protected for voltages from (VEE - 0.3V) to (VCC + 0.3V). The FORCE output also features a low-leakage, high-impedance state.

Integrated voltage clamps limit the force output to levels set externally. The force-current or the measure-current voltage can be offset -0.2V to +4.4V (IOS). This feature allows for the centering of the control or measured signal within the external DAC or ADC range.

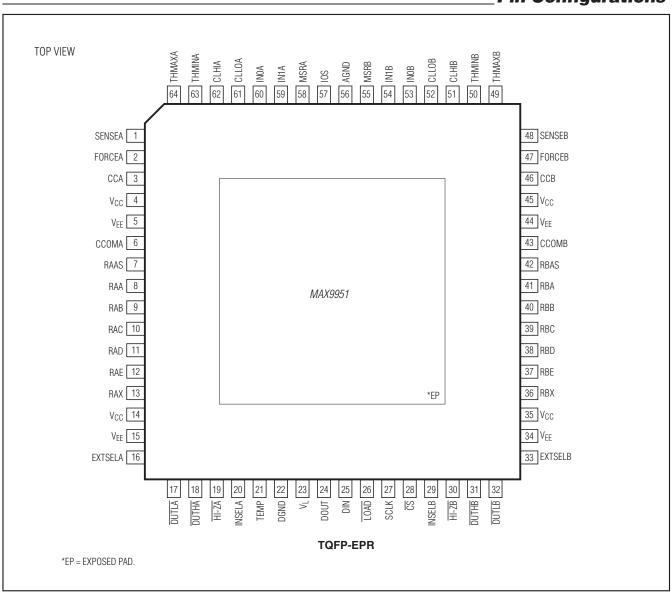

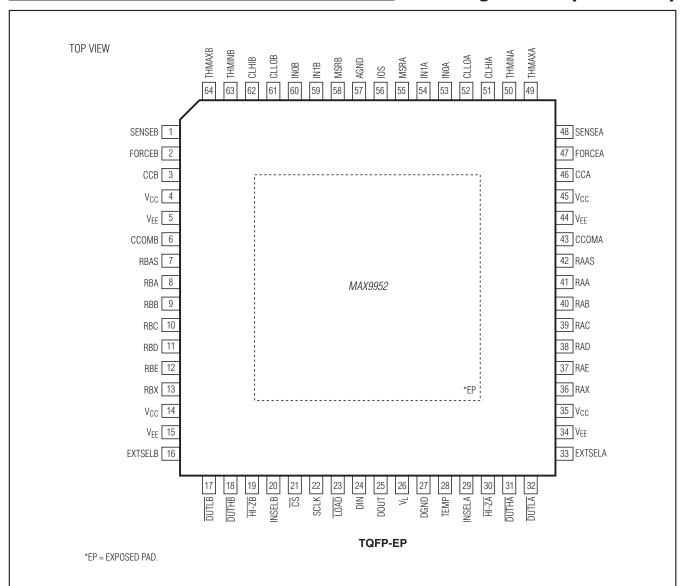

The MAX9951D/MAX9952D feature an integrated 10k $\Omega$  force-sense resistor between FORCE\_ and SENSE\_. The MAX9951F/MAX9952F have no internal force-sense resistor. These devices are available in a 64-pin, 10mm x 10mm, 0.5mm pitch TQFP package with an exposed 8mm x 8mm die pad on the top (MAX9951) or the bottom (MAX9952) of the package for efficient heat removal. The exposed pad is internally connected to VEE. The MAX9951/MAX9952 are specified over the commercial 0°C to +70°C temperature range.

### **Applications**

Memory Testers

VLSI Testers

System-on-a-Chip Testers

Structural Testers

Pin Configurations and Selector Guide appear at end of data sheet.

#### **Features**

- ◆ Force Voltage/Measure Current (FVMI)

- **♦** Force Current/Measure Voltage (FIMV)

- ♦ Force Voltage/Measure Voltage (FVMV)

- ♦ Force Current/Measure Current (FIMI)

- **♦** Force Nothing/Measure Voltage (FNMV)

- ◆ Force Nothing/Measure Current (FNMI, Range E Only)

- **♦** Termination/Measure Current

- **♦ Termination/Measure Voltage**

- **♦ Five Programmable Current Ranges**

- ±2µA

- ±20µA

- ±200μA

- ±2mÅ

- ±64mA

- → -2V to +7V Through -7V to +13V Input-Voltage Range

- Force-Current/Measure-Current Adjustable-Voltage Offset (IOS)

- ♦ Programmable Voltage Clamps at Force Output

- ♦ Low-Leakage, High-Impedance Measure, and Force States

- ♦ 3-Wire Serial Interface

- ♦ Low 6mA (max) Quiescent Current per PMU

### **Ordering Information**

| PART           | TEMP RANGE   | PIN-PACKAGE  |

|----------------|--------------|--------------|

| MAX9951DCCB+D  | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951DCCB+TD | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951DCCB-D  | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951DCCB-TD | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951FCCB+   | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951FCCB+T  | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951FCCB-D  | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9951FCCB-TD | 0°C to +70°C | 64 TQFP-EPR* |

| MAX9952DCCB+   | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952DCCB+T  | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952DCCB-D  | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952DCCB-TD | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952FCCB+   | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952FCCB+T  | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952FCCB-D  | 0°C to +70°C | 64 TQFP-EP** |

| MAX9952FCCB-TD | 0°C to +70°C | 64 TQFP-EP** |

|                |              |              |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>-</sup>Denotes a package containing lead(Pb).

D = Dry pack. \*EPR = Top side exposed pad.

T = Tape and reel. \*\*EP = Exposed pad.

## Dual Per-Pin Parametric Measurement Units

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND+20V                           | θ <sub>JC</sub> MAX9951_CCB (Note 1)+2°C/W           |

|-------------------------------------------------------|------------------------------------------------------|

| VEE to AGND15V                                        | θJA MAX9952_CCB (Note 1)+23°C/W                      |

| V <sub>CC</sub> to V <sub>EE</sub> +32V               | θ <sub>JC</sub> MAX9952_CCB (Note 1)+2°C/W           |

| V <sub>L</sub> to AGND+6V                             | Junction Temperature+150°C                           |

| AGND to DGND0.5V to +0.5V                             | Storage Temperature Range65°C to +150°C              |

| Digital Inputs/Outputs0.3V to (V <sub>L</sub> + 0.3V) | Operating Temperature Range (commercial)0°C to +70°C |

| All Other Pins to AGND(VEE - 0.3V) to (VCC + 0.3V)    | Lead Temperature (soldering, 10s)+300°C              |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Soldering Temperature (reflow)                       |

| MAX9951_CCB (derate 125mW/°C above +70°C)10,000mW     | Lead(Pb)-Free Packages+260°C                         |

| MAX9952_CCB (derate 43.5mW/°C above +70°C)3478mW      | Packages Containing Lead(Pb)+240°C                   |

| θ <sub>JA</sub> MAX9951_CCB (Note 1)+8°C/W            |                                                      |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.$  Specifications at  $T_A = T_{MIN}$  and  $T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C, unless$  otherwise noted.) (Note 2)

| PARAMETER                                         | SYMBOL                                   | CONDITIONS                                   |                                | MIN                   | TYP   | MAX                   | UNITS  |

|---------------------------------------------------|------------------------------------------|----------------------------------------------|--------------------------------|-----------------------|-------|-----------------------|--------|

| FORCE VOLTAGE                                     | •                                        |                                              |                                | •                     |       |                       |        |

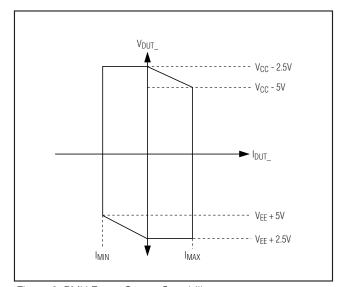

| Force Input Voltage<br>Range                      | V <sub>INO_</sub> ,<br>V <sub>IN1_</sub> |                                              |                                | V <sub>EE</sub> + 2.5 |       | V <sub>CC</sub> - 2.5 | V      |

|                                                   |                                          | DUT current at full scale                    | $V_{CC} = +12V, V_{EE} = -7V$  | -2                    |       | +7                    |        |

| Forced Voltage                                    | VDUT                                     | DOT current at full scale                    | $V_{CC} = +18V, V_{EE} = -12V$ | -7                    |       | +13                   | V      |

|                                                   |                                          | DUT current = 0A                             |                                | V <sub>EE</sub> + 2.5 |       | V <sub>CC</sub> - 2.5 |        |

| Input Bias Current                                |                                          |                                              |                                |                       | ±1    |                       | μΑ     |

| Forced-Voltage Offset                             | V <sub>FOS</sub>                         |                                              |                                | -25                   |       | +25                   | mV     |

| Forced-Voltage-Offset Temperature Coefficient     |                                          |                                              |                                |                       | ±100  |                       | μV/°C  |

| Forced-Voltage Gain<br>Error                      | VFGE                                     | Nominal gain of +1                           | Nominal gain of +1             |                       | 0.005 | +1                    | %      |

| Forced-Voltage-Gain<br>Temperature Coefficient    |                                          |                                              |                                |                       | ±10   |                       | ppm/°C |

| Forced-Voltage Linearity<br>Error                 | VFLER                                    | Gain and offset errors ca                    | librated out (Notes 3, 4)      | -0.02                 |       | +0.02                 | %FSR   |

| MEASURE CURRENT                                   |                                          |                                              |                                |                       |       |                       |        |

| Measure-Current Offset                            | I <sub>MOS</sub>                         | (Note 3)                                     |                                | -1                    |       | +1                    | %FSR   |

| Measure-Current-Offset<br>Temperature Coefficient |                                          |                                              |                                |                       | ±20   |                       | ppm/°C |

| Measure-Current Gain<br>Error                     | IMGE                                     | (Note 5)                                     |                                | -1                    |       | +1                    | %      |

| Measure-Current-Gain<br>Temperature Coefficient   |                                          |                                              |                                |                       | ±20   |                       | ppm/°C |

| Linearity Error                                   | I <sub>MLER</sub>                        | Gain and offset errors ca<br>(Notes 3, 4, 6) | librated out                   | -0.02                 |       | +0.02                 | %FSR   |

## **Dual Per-Pin Parametric Measurement Units**

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted. Specifications at <math>T_A = T_{MIN}$  and  $T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                                    | SYMBOL              | CONDITIONS                                            | MIN   | TYP    | MAX    | UNITS  |  |

|------------------------------------------------------------------------------|---------------------|-------------------------------------------------------|-------|--------|--------|--------|--|

| Measure-Output-Voltage<br>Range Over Full-Current                            | V <sub>MSR</sub> _  | V <sub>IOS</sub> = V <sub>DUTGND</sub>                | -4    |        | +4     | V      |  |

| Range                                                                        | * IVISI1_           | VIOS = 4V + VDUTGND                                   | 0     |        | +8     | ٧      |  |

| Current-Sense Amp<br>Offset-Voltage Input                                    | V <sub>IOS</sub>    | Relative to V <sub>DUTGND</sub>                       | -0.2  |        | +4.4   | V      |  |

| Rejection of Output-<br>Measure Error Due to<br>Common-Mode Sense<br>Voltage | CMVR <sub>LER</sub> | (Notes 5 and 7)                                       |       | +0.001 | +0.007 | %FSR/V |  |

|                                                                              |                     | Range E, R_E = $500k\Omega$                           | -2    |        | +2     |        |  |

|                                                                              |                     | Range D, R_D = $50k\Omega$                            | -20   |        | +20    | μΑ     |  |

| Measure-Current Range                                                        |                     | Range C, R_C = $5k\Omega$                             | -200  |        | +200   |        |  |

|                                                                              |                     | Range B, R_B = $500\Omega$                            | -2    |        | +2     |        |  |

|                                                                              |                     | Range A, R_A = $15.6\Omega$                           | -64   |        | +64    | mA     |  |

| FORCE CURRENT                                                                | •                   |                                                       | •     |        |        | •      |  |

| Input Voltage Range for                                                      | V <sub>INO_,</sub>  | VIOS = VDUTGND                                        | -4    |        | +4     | V      |  |

| Setting Forced Current Over Full Range                                       | V <sub>IN1</sub> _  | V <sub>IOS</sub> = 4V + V <sub>DUTGND</sub>           | 0     |        | +8     |        |  |

| Current-Sense Amp<br>Offset-Voltage Input                                    | V <sub>IOS</sub>    | Relative to V <sub>DUTGND</sub>                       | -0.2  |        | +4.4   | V      |  |

| IOS_ Input Bias Current                                                      |                     |                                                       |       | ±1     |        | μΑ     |  |

| Forced-Current Offset                                                        |                     | (Note 3)                                              | -1    |        | +1     | %FSR   |  |

| Forced-Current-Offset<br>Temperature Coefficient                             |                     |                                                       |       | ±20    |        | ppm/°C |  |

| Forced-Current Gain<br>Error                                                 |                     | (Note 5)                                              | -1    |        | +1     | %      |  |

| Forced-Current-Gain<br>Temperature Coefficient                               |                     |                                                       |       | ±20    |        | ppm/°C |  |

| Forced-Current Linearity<br>Error                                            | IFLER               | Gain and offset errors calibrated out (Notes 3, 4, 6) | -0.02 |        | +0.02  | %FSR   |  |

| Rejection of Output Error<br>Due to Common-Mode<br>Load Voltage              | CMRIOER             | (Notes 5 and 7)                                       |       | +0.001 | +0.007 | %FSR/V |  |

|                                                                              |                     | Range E, R_E = $500k\Omega$                           | -2    |        | +2     |        |  |

|                                                                              |                     | Range D, R_D = $50k\Omega$                            | -20   |        | +20    | μA     |  |

| Forced-Current Range                                                         |                     | Range C, R_C = $5k\Omega$                             | -200  |        | +200   |        |  |

|                                                                              |                     | Range B, R_B = $500\Omega$                            | -2    |        | +2     | - A    |  |

|                                                                              |                     | Range A, R_A = $15.6\Omega$                           | -64   |        | +64    | mA     |  |

## **Dual Per-Pin Parametric Measurement Units**

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.$  Specifications at  $T_A = T_{MIN}$  and  $T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                         | SYMBOL                                     | COND                                            | ITIONS                            | MIN                   | TYP    | MAX                   | UNITS       |

|---------------------------------------------------|--------------------------------------------|-------------------------------------------------|-----------------------------------|-----------------------|--------|-----------------------|-------------|

| MEASURE VOLTAGE                                   | •                                          | •                                               |                                   | •                     |        |                       |             |

| Measure-Voltage-Offset                            | V <sub>MOS</sub>                           |                                                 |                                   | -25                   |        | +25                   | mV          |

| Measure-Voltage-Offset<br>Temperature Coefficient |                                            |                                                 |                                   |                       | ±100   |                       | μV/°C       |

| Gain Error                                        | VMGER                                      | Nominal gain of +1                              |                                   | -1                    | ±0.005 | +1                    | %           |

| Measure-Voltage-Gain<br>Temperature Coefficient   |                                            |                                                 |                                   |                       | ±10    |                       | ppm/°C      |

| Measure-Voltage<br>Linearity Error                | VMLER                                      | Gain and offset errors ca<br>(Notes 3, 4, 6)    | librated out                      | -0.02                 |        | +0.02                 | %FSR        |

| Measure-Output-Voltage                            |                                            | DUT current at full scale VCC = +12V, VEE = -7V | -2                                |                       | +7     |                       |             |

| Range Over Full DUT                               | $V_{MSR}$                                  | DOT current at full scale                       | $V_{CC} = +18V$ , $V_{EE} = -12V$ | -7                    |        | +13                   | V           |

| Voltage                                           |                                            | DUT current = 0A                                |                                   | V <sub>EE</sub> + 2.5 |        | V <sub>CC</sub> - 2.5 |             |

| FORCE OUTPUT                                      | •                                          |                                                 |                                   |                       |        |                       |             |

| Off-State Leakage<br>Current                      |                                            |                                                 |                                   | -1                    |        | +1                    | nA          |

| Short-Circuit Current                             | I <sub>LIM</sub> -                         |                                                 |                                   | -92                   |        | -65                   | Л           |

| Limit                                             | I <sub>LIM+</sub>                          |                                                 |                                   | +65                   |        | +92                   | mA          |

| Force-to-Sense Resistor                           | R <sub>FS</sub>                            | D option only                                   |                                   | 8                     | 10     | 12                    | kΩ          |

| SENSE INPUT                                       |                                            |                                                 |                                   |                       |        |                       |             |

| Input Voltage Range                               |                                            |                                                 |                                   | V <sub>EE</sub> + 2.5 |        | V <sub>CC</sub> - 2.5 | V           |

| Leakage Current                                   |                                            | F option only                                   |                                   | -1                    |        | +1                    | nA          |

| COMPARATOR INPUTS                                 |                                            |                                                 |                                   |                       |        |                       |             |

| Input Voltage Range                               |                                            |                                                 |                                   | V <sub>EE</sub> + 2.5 |        | V <sub>CC</sub> - 2.5 | V           |

| Offset Voltage                                    |                                            |                                                 |                                   | -25                   |        | +25                   | mV          |

| Input Bias Current                                |                                            |                                                 |                                   |                       | ±1     |                       | μΑ          |

| VOLTAGE CLAMPS                                    |                                            |                                                 |                                   |                       |        |                       |             |

| Input Control Voltage                             | V <sub>CLLO_</sub> ,<br>V <sub>CLHI_</sub> |                                                 |                                   | V <sub>EE</sub> + 2.4 |        | V <sub>CC</sub> - 2.4 | V           |

| Clamp Voltage<br>Accuracy                         |                                            | (Note 8)                                        |                                   | -100                  |        | +100                  | mV          |

| DIGITAL INPUTS                                    | •                                          |                                                 |                                   |                       |        |                       |             |

| Input High Voltage (Note 9)                       |                                            | V <sub>L</sub> = 5V                             |                                   | +3.5                  |        |                       |             |

|                                                   | VIH                                        | V <sub>L</sub> = 3.3V                           |                                   | +2.0                  |        |                       | V           |

| (INOTE 3)                                         |                                            | $V_L = 2.5V$                                    |                                   | +1.7                  |        |                       |             |

| Input Low Voltage                                 | \/                                         | V <sub>L</sub> = 5V or 3.3V                     |                                   |                       |        | +0.8                  | 17          |

| (Note 9)                                          | VIL                                        | V <sub>L</sub> = 2.5V                           |                                   |                       |        | +0.7                  | →         ∨ |

| Input Current                                     | I <sub>IN</sub>                            |                                                 |                                   |                       | ±1     |                       | μΑ          |

| Input Capacitance                                 | CIN                                        |                                                 |                                   |                       | 3.0    |                       | рF          |

## **Dual Per-Pin Parametric Measurement Units**

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, T_A = +25^{\circ}C, unless otherwise noted. Specifications at <math>T_A = T_{MIN}$  and  $T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                            | CONDITIONS                                                       | MIN                   | TYP | MAX  | UNITS |

|-----------------------------------------|-----------------------------------|------------------------------------------------------------------|-----------------------|-----|------|-------|

| COMPARATOR OUTPUT                       | S                                 |                                                                  |                       |     |      | •     |

| Output High Voltage                     | VoH                               | $V_L = +2.375V \text{ to } +5.5V, R_{PUP} = 1k\Omega$            | V <sub>L</sub> - 0.2  |     |      | V     |

| Output Low Voltage                      | V <sub>OL</sub>                   | $V_L = +2.375V$ to +5.5V, $R_{PUP} = 1k\Omega$                   |                       |     | +0.4 | V     |

| High-Impedance-State<br>Leakage Current |                                   |                                                                  |                       | ±1  |      | μА    |

| High-Impedance-State Output Capacitance |                                   |                                                                  |                       | 6.0 |      | pF    |

| DIGITAL OUTPUTS                         | •                                 |                                                                  |                       |     |      | 1     |

| Output High Voltage                     | V <sub>OH</sub>                   | $I_{OUT} = 1$ mA, $V_L = +2.375$ V to $+5.5$ V, relative to DGND | V <sub>L</sub> - 0.25 |     |      | V     |

| Output Low Voltage                      | V <sub>OL</sub>                   | $I_{OUT}$ = -1mA, $V_L$ = +2.375V to +5.5V, relative to DGND     |                       |     | +0.2 | V     |

| POWER SUPPLY                            |                                   |                                                                  | ·                     |     |      |       |

| Positive Supply                         | Vcc                               | (Note 2)                                                         | +10                   | +12 | +18  | V     |

| Negative Supply                         | V <sub>EE</sub>                   | (Note 2)                                                         | -15                   | -7  | -5   | V     |

| Total Supply Voltage                    | V <sub>CC</sub> - V <sub>EE</sub> | (Note 10)                                                        |                       |     | +30  | V     |

| Logic Supply                            | VL                                |                                                                  | +2.375                |     | +5.5 | V     |

| Positive Supply Current                 | ICC                               | No load, clamps enabled                                          |                       |     | 10.0 | mA    |

| Negative Supply Current                 | IEE                               | No load, clamps enabled                                          |                       |     | 10.0 | mA    |

| Logic Supply Current                    | ΙL                                | No load, all digital inputs at rails                             |                       |     | 1.2  | mA    |

| Analog Ground Current                   | IAGND                             | No load, clamps enabled                                          |                       | 0.9 |      | mA    |

| Digital Ground Current                  | IDGND                             | No load, all digital inputs at rails                             |                       | 1.4 |      | mA    |

| Power-Supply Rejection                  | PSRR                              | 1MHz, measured at force output                                   |                       | 20  |      | - dB  |

| Ratio                                   | 1 31111                           | 60Hz, measured at force output                                   |                       | 85  |      |       |

# **Dual Per-Pin Parametric Measurement Units**

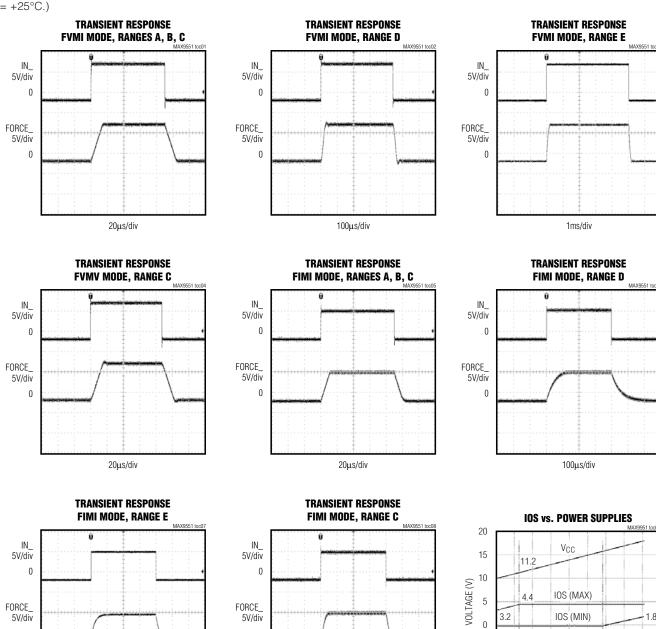

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, C_{CM} = 120pF, C_L = 100pF, T_A = +25^{\circ}C, unless otherwise noted. Specifications at T_A = T_{MIN} and T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                          | SYMBOL                  | CONDITIONS                                                                                                                    | MIN  | TYP  | MAX | UNITS |

|------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| FORCE VOLTAGE (Note                | s 10, 11)               |                                                                                                                               |      |      |     | -     |

|                                    |                         | Range E, R_E = $500k\Omega$                                                                                                   |      | 150  |     |       |

|                                    |                         | Range D, R_D = $50k\Omega$                                                                                                    |      | 50   |     |       |

| Settling Time                      |                         | Range C, R_C = $5k\Omega$                                                                                                     |      | 20   | 30  | μs    |

|                                    |                         | Range B, R_B = $500\Omega$                                                                                                    |      | 20   |     |       |

|                                    |                         | Range A, R_A = $15.6\Omega$                                                                                                   |      | 25   |     |       |

| FORCE VOLTAGE/MEAS                 | SURE CURF               | <b>RENT</b> (Notes 11, 12)                                                                                                    |      |      |     | •     |

|                                    |                         | Range E, R_E = $500k\Omega$                                                                                                   |      | 500  |     |       |

|                                    |                         | Range D, R_D = $50k\Omega$                                                                                                    |      | 100  |     |       |

| Settling Time                      |                         | Range C, R_C = $5k\Omega$                                                                                                     |      | 30   | 55  | μs    |

|                                    |                         | Range B, R_B = $500\Omega$                                                                                                    |      | 25   |     |       |

|                                    |                         | Range A, R_A = $15.6\Omega$                                                                                                   |      | 25   |     | 1     |

| Range Change<br>Switching          |                         | In addition to force-voltage and measure-current settling times, range A to range B, R_A = 15.6 $\Omega$ , R_B = 500 $\Omega$ |      | 12   |     | μs    |

| FORCE CURRENT/MEAS                 | SURE VOLT               | <b>FAGE</b> (Notes 11, 12)                                                                                                    |      |      |     |       |

|                                    |                         | Range E, R_E = $500k\Omega$                                                                                                   |      | 2500 |     |       |

|                                    |                         | Range D, R_D = $50k\Omega$                                                                                                    |      | 350  |     | ]     |

| Settling Time                      |                         | Range C, R_C = $5k\Omega$                                                                                                     |      | 30   | 60  | μs    |

|                                    |                         | Range B, R_B = $500\Omega$                                                                                                    |      | 25   |     | 1     |

|                                    |                         | Range A, R_A = $15.6\Omega$                                                                                                   |      | 25   |     | 1     |

| Range Change<br>Switching          |                         | In addition to force-current and measure-voltage settling times, range A to range B, R_A = 15.6 $\Omega$ , R_B = 500 $\Omega$ |      | 12   |     | μs    |

| SENSE INPUT TO MEAS                | URE OUTP                | UT PATH                                                                                                                       |      |      |     | •     |

| Propagation Delay                  |                         | C <sub>LMSR</sub> = 100pF                                                                                                     |      | 0.2  |     | μs    |

| MEASURE OUTPUT                     |                         |                                                                                                                               |      |      |     | •     |

| Maximum Stable Load<br>Capacitance |                         |                                                                                                                               | 1000 |      |     | pF    |

| COMPARATORS (CLCOM                 | ир = 20pF, F            | $RPUP = 1k\Omega$ )                                                                                                           |      |      |     |       |

| Propagation Delay                  |                         | 50mV overdrive, 1V <sub>P-P</sub> , measured from input-<br>threshold zero crossing to 50% of output voltage<br>(Note 13)     |      | 75   |     | ns    |

| Rise Time                          |                         | 20% to 80%                                                                                                                    |      | 60   |     | ns    |

| Fall Time                          |                         | 80% to 20%                                                                                                                    |      | 5    |     | ns    |

| SERIAL PORT (V <sub>L</sub> = +3.3 | BV, C <sub>DOUT</sub> = | = 10pF)                                                                                                                       |      |      |     | 1     |

| Serial Clock Frequency             | fSCLK                   | (Note 14)                                                                                                                     |      |      | 20  | MHz   |

| SCLK Pulse-Width High              | tCH                     | ,                                                                                                                             | 12   |      |     | ns    |

| SCLK Pulse-Width Low               | tCL                     |                                                                                                                               | 12   |      |     | ns    |

### Dual Per-Pin Parametric Measurement Units

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +12V, V_{EE} = -7V, V_L = +3.3V, C_{CM} = 120pF, C_L = 100pF, T_A = +25^{\circ}C, unless otherwise noted. Specifications at T_A = T_{MIN}$  and  $T_A = T_{MAX}$  are guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                            | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------------------------|------------------|------------|-----|-----|-----|-------|

| SCLK Fall to DOUT Valid                              | t <sub>DO</sub>  |            |     |     | 22  | ns    |

| CS Low to SCLK High<br>Setup                         | tcsso            |            | 10  |     |     | ns    |

| SCLK High to $\overline{\text{CS}}$ High Hold        | tCSH1            |            | 22  |     |     | ns    |

| SCLK High to $\overline{\text{CS}}$ Low Hold         | tCSH0            |            | 0   |     |     | ns    |

| CS High to SCLK High<br>Setup                        | tCSS1            |            | 5   |     |     | ns    |

| DIN to SCLK High Setup                               | t <sub>DS</sub>  |            | 10  |     |     | ns    |

| DIN to SCLK High Hold                                | t <sub>DH</sub>  | (Note 13)  | 0   |     |     | ns    |

| CS Pulse-Width High                                  | tcswh            |            | 10  |     |     | ns    |

| CS Pulse-Width Low                                   | tcswl            |            | 10  |     |     | ns    |

| LOAD Pulse-Width Low                                 | t <sub>LDW</sub> |            | 20  |     | •   | ns    |

| V <sub>DD</sub> High to <del>CS</del> Low (Power-Up) |                  | (Note 13)  |     |     | 500 | ns    |

- Note 2: The device operates properly with different supply voltages with equally different voltage swings.

- **Note 3:** Interpret errors expressed in terms of %FSR (percent of full-scale range) as a percentage of the end-point-to-end-point range, i.e., for the ±64mA range, the full-scale range = 128mA, and a 1% error = 1.28mA.

- **Note 4:** Case must be maintained ±5°C for linearity specifications.

- Note 5: Tested in range C.

- Note 6: Current linearity specifications are maintained to within 700mV of the clamp voltages when the clamps are enabled.

- Note 7: Specified as the percent of full-scale range change at the output per volt change in the DUT voltage.

- Note 8: V<sub>CLLO</sub> and V<sub>CLHI</sub> should differ by at least 700mV.

- Note 9: The digital interface accepts +5V, +3.3V, and +2.5V CMOS logic levels. The voltage at V<sub>L</sub> adjusts the threshold.

- Note 10: Guaranteed by design.

- **Note 11:** Settling times are to 0.1% of FSR.  $C\chi_{-}$  = 60pF.

- **Note 12:** All settling times are specified using a single compensation capacitor (Cx\_) across all current-sense resistors. Use an individual capacitor across each sense resistor for better performance across all current ranges, particularly the lower ranges.

- **Note 13:** The propagation delay time is only guaranteed over the force-voltage output range. Propagation delay is measured by holding V<sub>SENSE</sub> steady and transitioning THMAX\_ or THMIN\_.

- **Note 14:** Maximum serial clock frequency may diminish at V<sub>L</sub> < +3.3V.

2ms/div

## Dual Per-Pin Parametric Measurement Units

### Typical Operating Characteristics

-0.2

-7

VEE

-5

-10 -15

$(V_{CC} = +12V, V_{EE} = -7V, C_L = 100pF, C_{CM} = 120pF, C_{CX} = 60pF, R_L \ to \ +2.5V, \ range \ A: R_A = 15.6\Omega, R_L = 70.3\Omega; \ range \ B: R_B = 500\Omega, R_L = 2.25k\Omega; \ range \ C: R_C = 5k\Omega, R_L = 22.5k\Omega; \ range \ D: R_D = 50k\Omega, R_L = 225k\Omega; \ range \ E: R_E = 500k\Omega, R_L = 2.25M\Omega, T_A = +25^{\circ}C. )$

8 Maxim Integrated

40µs/div

# **Dual Per-Pin Parametric Measurement Units**

### **Pin Description**

| PIN              |                  |         |                                                                                                                                                                                          |

|------------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9951          | MAX9952          | NAME    | FUNCTION                                                                                                                                                                                 |

| 1                | 48               | SENSEA  | PMU-A Sense Input. A Kelvin connection to the DUT. Provides the feedback signal in FVMI mode and the measured signal in FIMV mode for PMU-A.                                             |

| 2                | 47               | FORCEA  | PMU-A Driver Output. Forces a current or voltage to the DUT for PMU-A.                                                                                                                   |

| 3                | 46               | CCA     | PMU-A Compensation Capacitor Connection. Provides compensation for the PMU-A main amplifier. Connect a 120pF capacitor from CCA to CCOMA.                                                |

| 5, 15,<br>34, 44 | 5, 15,<br>34, 44 | VEE     | Negative Analog-Supply Input                                                                                                                                                             |

| 4, 14,<br>35, 45 | 4, 14,<br>35, 45 | Vcc     | Positive Analog-Supply Input                                                                                                                                                             |

| 6                | 43               | CCOMA   | Common Connection of CMA and CXA for PMU-A                                                                                                                                               |

| 7                | 42               | RAAS    | PMU-A Range Setting Resistor-Sense Connection                                                                                                                                            |

| 8                | 41               | RAA     | PMU-A Range A Setting Resistor Connection                                                                                                                                                |

| 9                | 40               | RAB     | PMU-A Range B Setting Resistor Connection                                                                                                                                                |

| 10               | 39               | RAC     | PMU-A Range C Setting Resistor Connection                                                                                                                                                |

| 11               | 38               | RAD     | PMU-A Range D Setting Resistor Connection                                                                                                                                                |

| 12               | 37               | RAE     | PMU-A Range E Setting Resistor Connection                                                                                                                                                |

| 13               | 36               | RAX     | PMU-A Current-Range Sense-Resistor Connection. Connects to the external current range sense resistor for PMU-A.                                                                          |

| 16               | 33               | EXTSELA | PMU-A External Current-Range Selector. Selects the external current range for PMU-A.                                                                                                     |

| 17               | 32               | DUTLA   | PMU-A Window Comparator Lower Comparator Output. A high output indicates that the sensed voltage at the window comparator is above V <sub>THMINA</sub> . DUTLA is an open-drain output.  |

| 18               | 31               | DUTHA   | PMU-A Window Comparator Higher Comparator Output. A high output indicates that the sensed voltage at the window comparator is below V <sub>THMAXA</sub> . DUTHA is an open-drain output. |

| 19               | 30               | HI-ZA   | MSRA Tri-State Control Input. A logic-low places MSRA in a high-impedance state.                                                                                                         |

| 20               | 29               | INSELA  | Input Select PMU-A. INSELA is a logic input that selects between IN0A and IN1A. Force INSELA low to select IN0A. INSELA is OR'ed with control register bit INMODEA.                      |

| 21               | 28               | TEMP    | Temperature Output. V <sub>TEMP</sub> = 10mV/°C. T <sub>DIE</sub> (°C) = (100)V <sub>TEMP</sub> - 273.                                                                                   |

| 22               | 27               | DGND    | Digital Ground                                                                                                                                                                           |

| 23               | 26               | VL      | Logic-Supply Voltage Input. The voltage applied at V <sub>L</sub> sets the upper logic-voltage level.                                                                                    |

| 24               | 25               | DOUT    | Serial-Data Output. A standard SPI™-compatible output.                                                                                                                                   |

| 25               | 24               | DIN     | Serial-Data Input                                                                                                                                                                        |

| 26               | 23               | LOAD    | Serial-Port Load Input. A logic-low asynchronously loads data from the input registers into the PMU registers.                                                                           |

SPI is a trademark of Motorola, Inc.

# **Dual Per-Pin Parametric Measurement Units**

### Pin Description (continued)

| PIN     |         |         |                                                                                                                                                                                          |

|---------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9951 | MAX9952 | NAME    | FUNCTION                                                                                                                                                                                 |

| 27      | 22      | SCLK    | Serial-Clock Input. SCLK accepts external clock frequencies up to 20MHz.                                                                                                                 |

| 28      | 21      | CS      | Chip-Select Input. Force $\overline{\text{CS}}$ low to enable the serial interface.                                                                                                      |

| 29      | 20      | INSELB  | Input Select PMU-B. INSELB is a logic input that selects between IN0B and IN1B. Force INSELB low to select IN0B. INSELB is OR'ed with control register bit INMODEB.                      |

| 30      | 19      | HI-ZB   | MSRB Tri-State Control Input. A logic-low places MSRB in a high-impedance state.                                                                                                         |

| 31      | 18      | DUTHB   | PMU-B Window Comparator Higher Comparator Output. A high output indicates that the sensed voltage at the window comparator is below V <sub>THMAXB</sub> . DUTHB is an open-drain output. |

| 32      | 17      | DUTLB   | PMU-B Window Comparator Lower Comparator Output. A high output indicates that the sensed voltage at the window comparator is above V <sub>THMINB</sub> . DUTLB is an open-drain output.  |

| 33      | 16      | EXTSELB | PMU-B External Current-Range Selector. Selects the external current range for PMU-B.                                                                                                     |

| 36      | 13      | RBX     | PMU-B Current-Range Sense-Resistor Connection. Connects to the external current-range sense resistor for PMU-B.                                                                          |

| 37      | 12      | RBE     | PMU-B Range E Setting Resistor Connection                                                                                                                                                |

| 38      | 11      | RBD     | PMU-B Range D Setting Resistor Connection                                                                                                                                                |

| 39      | 10      | RBC     | PMU-B Range C Setting Resistor Connection                                                                                                                                                |

| 40      | 9       | RBB     | PMU-B Range B Setting Resistor Connection                                                                                                                                                |

| 41      | 8       | RBA     | PMU-B Range A Setting Resistor Connection                                                                                                                                                |

| 42      | 7       | RBAS    | PMU-B Range A Setting Resistor-Sense Connection                                                                                                                                          |

| 43      | 6       | CCOMB   | Common Connection of CMB and CXB for PMU-B                                                                                                                                               |

| 46      | 3       | CCB     | PMU-B Compensation Capacitor Connection. Provides compensation for the PMU-B main amplifier. Connect a 120pF capacitor from CCB to CCOMB.                                                |

| 47      | 2       | FORCEB  | PMU-B Driver Output. Forces a current or voltage to the DUT for PMU-B.                                                                                                                   |

| 48      | 1       | SENSEB  | PMU-B Sense Input. A Kelvin connection to the DUT. Provides the feedback signal in FVMI mode and the measured signal in FIMV mode for PMU-B.                                             |

| 49      | 64      | THMAXB  | PMU-B Window Comparator Upper Threshold Voltage Input. Sets the upper voltage threshold for the PMU-B window comparator.                                                                 |

| 50      | 63      | THMINB  | PMU-B Window Comparator Lower Threshold Voltage Input. Sets the lower voltage threshold for the PMU-B window comparator.                                                                 |

| 51      | 62      | CLHIB   | PMU-B Upper-Clamp Voltage Input. Sets the upper-clamp voltage level.                                                                                                                     |

| 52      | 61      | CLLOB   | PMU-B Lower-Clamp Voltage Input. Sets the lower-clamp voltage level.                                                                                                                     |

| 53      | 60      | IN0B    | Force-Threshold Current Input for PMU-B. Sets the forced voltage in FV mode or the forced current in FI mode.                                                                            |

| 54      | 59      | IN1B    | Force-Threshold Voltage Input for PMU-B. Sets the forced voltage in FV mode or the forced current in FI mode                                                                             |

# **Dual Per-Pin Parametric Measurement Units**

### Pin Description (continued)

| Pi      | PIN     |        | FUNCTION                                                                                                                                                                                                                      |  |

|---------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX9951 | MAX9952 | NAME   | FUNCTION                                                                                                                                                                                                                      |  |

| 55      | 58      | MSRB   | PMU-B Measurement Output. Provides a voltage equal to the SENSE voltage in FIMV mode, and provides a voltage proportional to the DUT current in FVMI mode for PMU-B. Force HI-ZB low to place MSRB in a high-impedance state. |  |

| 56      | 57      | AGND   | Analog Ground                                                                                                                                                                                                                 |  |

| 57      | 56      | IOS    | Offset-Voltage Input. Sets an offset voltage for the internal current-sense amplifiers of both channels.                                                                                                                      |  |

| 58      | 55      | MSRA   | PMU-A Measurement Output. Provides a voltage equal to the SENSE voltage in FIMV mode, and provides a voltage proportional to the DUT current in FVMI mode for PMU-A. Force HI-ZA low to place MSRA in a high-impedance state. |  |

| 59      | 54      | IN1A   | Force-Threshold Voltage Input for PMU-A. Sets the forced voltage in FV mode or the forced current in FI mode.                                                                                                                 |  |

| 60      | 53      | INOA   | Force-Threshold Current Input for PMU-A. Sets the forced voltage in FV mode or the forced current in FI mode.                                                                                                                 |  |

| 61      | 52      | CLLOA  | PMU-A Lower-Clamp Voltage Input. Sets the lower-clamp voltage level.                                                                                                                                                          |  |

| 62      | 51      | CLHIA  | PMU-A Upper-Clamp Voltage Input. Sets the upper-clamp voltage level.                                                                                                                                                          |  |

| 63      | 50      | THMINA | PMU-A Window Comparator Lower Threshold Voltage Input. Sets the lower voltage threshold for the PMU-A window comparator.                                                                                                      |  |

| 64      | 49      | THMAXA | PMU-A Window Comparator Upper Threshold Voltage Input. Sets the upper voltage threshold for the PMU-A window comparator.                                                                                                      |  |

| _       | _       | EP     | Exposed Pad. Internally biased to V <sub>EE</sub> . Connect to a large ground plane or heatsink to maximize thermal performance. Not intended as an electrical connection point.                                              |  |

# **Dual Per-Pin Parametric Measurement Units**

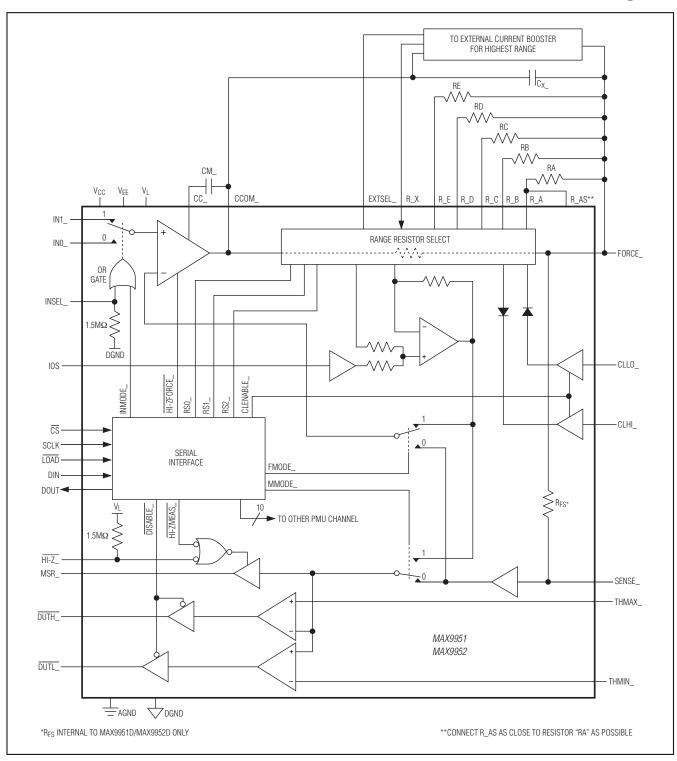

### **Functional Diagram**

### Dual Per-Pin Parametric Measurement Units

### **Detailed Description**

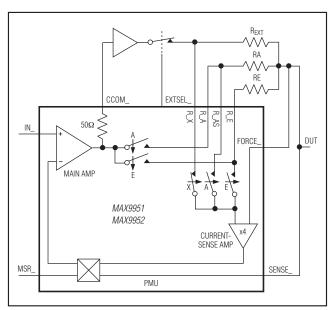

The MAX9951/MAX9952 force or measure voltages in the -2V to +7V through -7V to +13V ranges, dependent upon the supply voltage range (VCC and VEE). These devices also force or measure currents up to  $\pm 64$ mA, with a lowest full-scale range of  $\pm 2\mu$ A. Use an external buffer amplifier for current ranges greater than  $\pm 64$ mA.

MSR\_ presents a voltage proportional to the measured voltage or current. Place MSR\_ in a low-leakage, high-impedance state by forcing HI-Z\_ low. Integrated comparators with externally programmable voltage thresholds provide "too low" (DUTL\_) and "too high" (DUTH\_) voltage-monitoring outputs. Each comparator output features a selectable high-impedance state. The devices feature separate FORCE\_ and SENSE\_ connections and are fully protected against short circuits. The FORCE\_ output has two voltage clamps, negative (CLLO\_) and positive (CLHI\_), to limit the voltage to externally provided levels. Two control-voltage inputs, selected independently of the PMU mode, allow for greater flexibility.

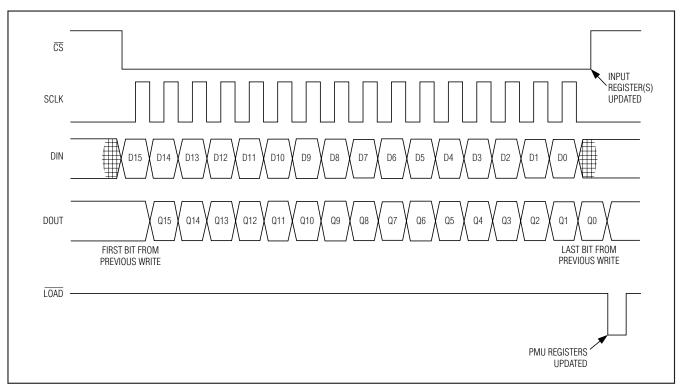

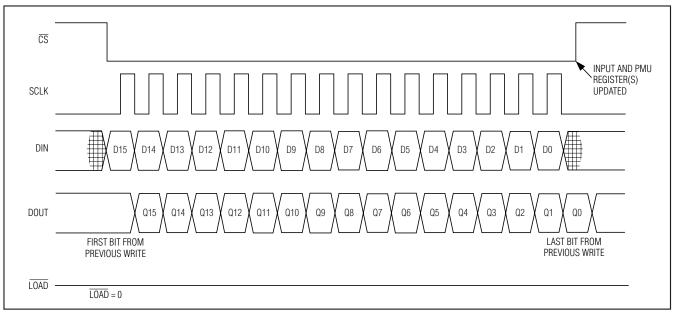

### Serial Interface

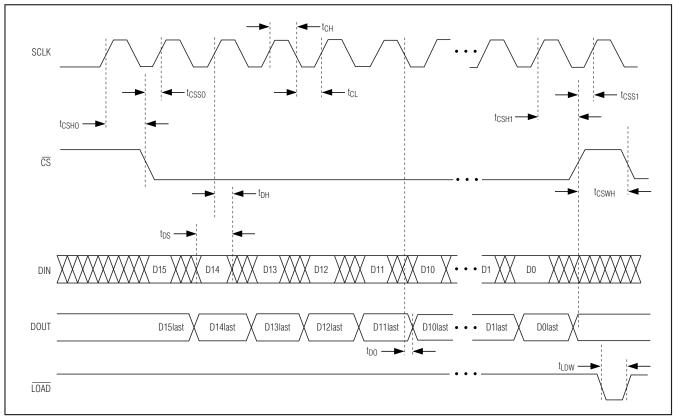

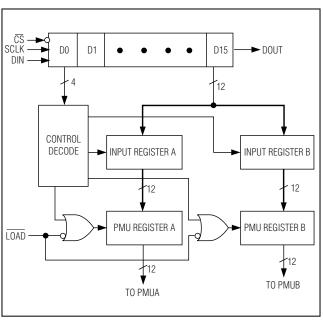

The MAX9951/MAX9952 use a standard 3-wire SPI/QSPI™/MICROWIRE™-compatible serial port. Once the input data register fills, the data becomes available at DOUT. This data output allows for daisy-chaining multiple devices. Figures 1, 2, and 3 show the serial interface timing diagrams.

### Serial Port Operation

The serial interface has two ranks (Figure 4). Each PMU has an input register that loads from the serial port shift register. Each PMU also has a PMU register that loads from the input register. Data does not affect the PMU until it reaches the PMU register. This register configuration permits loading of the PMU data into the input register at one time and then latching the input register data into the PMU register later, at which time the PMU function changes accordingly. The register configuration also provides the ability to change the state of the PMU asynchronously, with respect to the loading of that PMU's data into the serial port. Thus, the PMU easily updates simultaneously with other PMUs or other devices.

Figure 1. Serial Port Timing with Asynchronous Load

QSPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

## **Dual Per-Pin Parametric Measurement Units**

Figure 2. Serial Port Timing with Synchronous Load

Figure 3. Detailed Serial Port Timing Diagram

## **Dual Per-Pin Parametric Measurement Units**

Figure 4. Dual PMU Serial Port Block Diagram

Use  $\overline{\text{LOAD}}$  to asynchronously load all input registers into the PMU registers. If  $\overline{\text{LOAD}}$  remains low when data latches into an input register, the data also transfers to the PMU register.

#### **PMU Control**

Programming both PMUs with the same data requires a 16-bit word. Programming each PMU with separate data requires two 16-bit words.

The address bits specify which input registers the shift-register loads. Table 2 describes the function of the address bits.

Bits C1 and C2 specify how the data loads into the second rank PMU registers. These 2 control bits serve a similar function as the  $\overline{\text{LOAD}}$  input. The specified actions occur when  $\overline{\text{CS}}$  goes high, whereas the  $\overline{\text{LOAD}}$  input loads the PMU register at anytime. When either C1 or C2 is low, the corresponding PMU register is transparent. Table 3 describes the function of the 2 control bits.

The NOP operation requires A1 = A2 = C1 = C2 = 0. In this case, the data transfers through the shift register without changing the state of the device.

### **Table 1. Bit Assignments**

| BIT | BIT NAME  |

|-----|-----------|

| 15  | INMODE    |

| 14  | FMODE     |

| 13  | MMODE     |

| 12  | RS2       |

| 11  | RS1       |

| 10  | RS0       |

| 9   | CLENABLE  |

| 8   | HI-ZFORCE |

| 7   | HI-ZMSR   |

| 6   | DISABLE   |

| 5   | B2        |

| 4   | B1        |

| 3   | A2        |

| 2   | A1        |

| 1   | C2        |

| 0   | C1        |

#### Table 2. Address Bit

| A2 | A1 | OPERATION                                       |

|----|----|-------------------------------------------------|

| 0  | 0  | Do not update any input register (NOP).         |

| 0  | 1  | Only update input register A.                   |

| 1  | 0  | Only update input register B.                   |

| 1  | 1  | Update both input registers with the same data. |

### Table 3. Control Bit

| C2 | C1 | OPERATION                                           |

|----|----|-----------------------------------------------------|

| 0  | 0  | Data stays in input register.                       |

| 0  | 1  | Transfer PMU-A input register to PMU register.      |

| 1  | 0  | Transfer PMU-B input register to PMU register.      |

| 1  | 1  | Transfer both input registers to the PMU registers. |

## Dual Per-Pin Parametric Measurement Units

C1 = C2 = 0 allows for data transfer from the shift register to the input register without transferring data to the PMU register (unless  $\overline{\text{LOAD}}$  is low). This permits the latching of data into the PMU register at a later time by  $\overline{\text{LOAD}}$  or subsequent command. Table 4 summarizes the possible control and address bit combinations. When asynchronously latching only one PMU's data, the input register of the other PMU maintains the same data. Therefore, loading both PMU registers would update the one PMU with new data while the other PMU remains in its current state.

#### **Mode Selection**

Four bits from the control word select between the various force-measure modes of operation. INMODE selects between the two input analog control voltages. FMODE selects whether the PMU forces a voltage or a current. MMODE selects whether the DUT current or DUT voltage is directed to MSR\_. HI-ZFORCE places the driver amplifier in a high-output-impedance state. Table 5 describes the various force and measure modes of operation.

**Table 4. PMU Operation Using Control and Address Bits**

| A2 | A1 | C2 | C1 | PMU-A OPERATION                                                   | PMU-B OPERATION                                                   |  |

|----|----|----|----|-------------------------------------------------------------------|-------------------------------------------------------------------|--|

| 0  | 0  | 0  | 0  | NOP: data just passes through                                     |                                                                   |  |

| 0  | 0  | 0  | 1  | Transfer PMU register A from input register A.                    | NOP.                                                              |  |

| 0  | 0  | 1  | 0  | NOP.                                                              | Transfer PMU register B from input register B.                    |  |

| 0  | 0  | 1  | 1  | Transfer PMU register A from input register A.                    | Transfer PMU register B from input register B.                    |  |

| 0  | 1  | 0  | 0  | Transfer input register A from shift register.                    | NOP.                                                              |  |

| 0  | 1  | 0  | 1  | Transfer input register A and PMU register A from shift register. | NOP.                                                              |  |

| 0  | 1  | 1  | 0  | Transfer input register A from shift register.                    | Transfer PMU register B from input register B.                    |  |

| 0  | 1  | 1  | 1  | Transfer input register A and PMU register A from shift register. | Transfer PMU register B from input register B.                    |  |

| 1  | 0  | 0  | 0  | NOP.                                                              | Transfer input register B from shift register.                    |  |

| 1  | 0  | 0  | 1  | Transfer PMU register A from input register A.                    | Transfer input register B from shift register.                    |  |

| 1  | 0  | 1  | 0  | NOP.                                                              | Transfer input register B and PMU register B from shift register. |  |

| 1  | 0  | 1  | 1  | Transfer PMU register A from input register A.                    | Transfer input register B and PMU register B from shift register. |  |

| 1  | 1  | 0  | 0  | Transfer input register A from shift register.                    | Transfer input register B from shift register.                    |  |

| 1  | 1  | 0  | 1  | Transfer input register A and PMU register A from shift register. | Transfer input register B from shift register.                    |  |

| 1  | 1  | 1  | 0  | Transfer input register A from shift register.                    | Transfer input register B and PMU register B from shift register. |  |

| 1  | 1  | 1  | 1  | Transfer input register A and PMU register A from shift register. | Transfer input register B and PMU register B from shift register. |  |

### Dual Per-Pin Parametric Measurement Units

Table 5. PMU Force-Measure Mode Selection

| INMODE* | FMODE | MMODE | HI-ZFORCE | PMU MODE               | FORCE<br>OUTPUT    | MEASURE<br>OUTPUT | ACTIVE<br>INPUT  |

|---------|-------|-------|-----------|------------------------|--------------------|-------------------|------------------|

| 0       | 0     | 1     | 1         | FVMI                   | Voltage            | IDUT              | VINO             |

| 1       | 0     | 1     | 1         | FVMI                   | Voltage            | IDUT              | V <sub>IN1</sub> |

| 0       | 0     | 0     | 1         | FVMV                   | Voltage            | V <sub>DUT</sub>  | VINO             |

| 1       | 0     | 0     | 1         | FVMV                   | Voltage            | V <sub>DUT</sub>  | V <sub>IN1</sub> |

| 0       | 1     | 1     | 1         | FIMI                   | Current            | IDUT              | VINO             |

| 1       | 1     | 1     | 1         | FIMI                   | Current            | IDUT              | V <sub>IN1</sub> |

| 0       | 1     | 0     | 1         | FIMV                   | Current            | V <sub>DUT</sub>  | VINO             |

| 1       | 1     | 0     | 1         | FIMV                   | Current            | V <sub>DUT</sub>  | V <sub>IN1</sub> |

| X       | 0     | 1     | 0         | FNMI<br>(range E only) | High-<br>Impedance | I <sub>DUT</sub>  | ×                |

| X       | 0     | 0     | 0         | FNMV                   | High-<br>Impedance | V <sub>DUT</sub>  | X                |

| 0       | 1     | 0     | 0         | Termination            | Voltage            | V <sub>DUT</sub>  | VINO             |

| 1       | 1     | 0     | 0         | Termination            | Voltage            | V <sub>DUT</sub>  | V <sub>IN1</sub> |

| 0       | 1     | 1     | 0         | Termination            | Voltage            | IDUT              | VINO             |

| 1       | 1     | 1     | 0         | Termination            | Voltage            | IDUT              | V <sub>IN1</sub> |

$<sup>*</sup>INSEL_{-} = 0$

**Table 6. Current-Range Selection**

| <u> </u> |     |     |          |                                   |

|----------|-----|-----|----------|-----------------------------------|

| RS2      | RS1 | RS0 | RANGE    | NOMINAL RESISTOR VALUE $(\Omega)$ |

| 0        | 0   | Χ   | ±2µA     | R_E = 500k                        |

| 0        | 1   | 0   | ±20µA    | $R_D = 50k$                       |

| 0        | 1   | 1   | ±200µA   | R_C = 5k                          |

| 1        | 0   | 0   | ±2mA     | R_B = 500                         |

| 1        | Χ   | 1   | ±64mA    | R_A = 15.6                        |

| 1        | 1   | 0   | External | _                                 |

Table 7. MSR\_ Output Truth Table

|         | -     |                        |

|---------|-------|------------------------|

| HI-ZMSR | HI-Z_ | MSR_                   |

| 1       | 1     | Measure output enabled |

| 0       | 1     | High impedance         |

| 1       | 0     | High impedance         |

| 0       | 0     | High impedance         |

### **Current-Range Selection**

Three bits from the control word, RS0, RS1, and RS2, control the full-scale current range for either FI (force current) or MI (measure current). Table 6 describes the full-scale current-range control.

#### Clamp Enable

The CLENABLE bit enables the force-output-voltage clamps when high and disables the clamps when low. There is hysteresis equal to approximately 5% of the current range for clamp when serial bit B1 is 1. For bit B1 = 0, no hysteresis, but clamp voltage is less accurate.

#### Measure Output High-Impedance Control

MSR\_ attains a low-leakage, high-impedance state by using the HI-ZMSR control bit, or the HI-Z\_ input. HI-Z\_ is internally pulled up to V\_ with a 1.5M $\Omega$  resistor. The 2 bits are logically ANDed together to control the MSR\_ output. HI-Z\_ allows external multiplexing among several PMU MSR\_ outputs without using the serial interface. Table 7 explains the various output modes for the MSR\_ output.

#### **Digital Output (DOUT)**

The digital output follows the last output of the serial-shift register and clocks out on the falling edge of SCLK. DOUT serially shifts the first bit of the incoming serial data word 16.5 clock cycles later. This allows for daisy-chaining additional devices using DOUT and the same clock.

## Dual Per-Pin Parametric Measurement Units

### "Quick Load" Using Chip Select

If  $\overline{\text{CS}}$  goes low and then returns high without any clock activity, the data from the input registers latch into the PMU registers. This extra function is not standard for SPI/QSPI/MICROWIRE interfaces. The quick load mimics the function of  $\overline{\text{LOAD}}$  without forcing  $\overline{\text{LOAD}}$  low.

### **Comparators**

Two comparators configured as a window comparator monitor MSR\_. THMAX\_ and THMIN\_ set the high and low thresholds that determine the window. Both outputs are open drain and share a single disable control that places the outputs in a high-impedance, low-leakage state. Table 8 describes the comparator output states of the MAX9951/MAX9952.

### \_Applications Information

In force-voltage (FV) mode, the voltage at FORCE\_ is directly proportional to the input control voltage. In force-current (FI) mode, the current flowing out of FORCE\_ is proportional to the input control voltage. Positive current flows out of the PMU.

In force-nothing (FN) mode, FORCE\_ is high impedance. In measure-current (MI) mode, the voltage at MSR\_ is directly proportional to the current exiting FORCE\_. Positive current flows out of the PMU.

In measure-voltage (MV) mode, the voltage at MSR\_ is directly proportional to the voltage at SENSE\_.

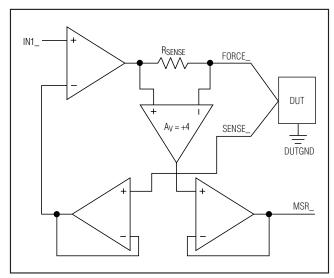

## Current-Sense-Amplifier Offset-Voltage Input

IOS is a buffered input to the current-sense amplifiers. The current-sense amplifiers convert the input control voltage (IN0\_ or IN1\_) to the forced DUT current (FI),

**Table 8. Comparator Truth Table**

| DISABLE | CONDITION                                                       | DUTH_  | DUTL_  |

|---------|-----------------------------------------------------------------|--------|--------|

| 0       | X                                                               | High-Z | High-Z |

| 1       | V <sub>MSR_</sub> > V <sub>THMAX_</sub> and V <sub>THMIN_</sub> | 0      | 1      |

| 1       | VTHMAX_ > VMSR_ > VTHMIN_                                       | 1      | 1      |

| 1       | VTHMAX_ and VTHMIN_ > VMSR_                                     | 1      | 0      |

| 1       | VTHMIN_ > VMSR_ > VTHMAX_*                                      | 0      | 0      |

<sup>\*</sup>V<sub>THMAX\_</sub> > V<sub>THMIN\_</sub> constitutes normal operation. This condition, however, has V<sub>THMIN\_</sub> > V<sub>THMAX\_</sub> and does not cause any problems with the operation of the comparators.

and convert the sensed DUT current to the MSR\_ output voltage (MI). When IOS equals zero relative to DUTGND (the GND voltage at the DUT, which the level-setting DACs and the ADC are presumed to use as a ground reference), the nominal voltage range that corresponds to ±full-scale current is -4V to +4V. Any voltage applied to IOS adds directly to this control input/measure output voltage range, i.e., applying +4V to IOS forces the voltage range that corresponds to ±full-scale current from 0 to +8V.

The following equations determine the minimum and maximum currents for each current range corresponding to the input voltage or measure voltage:

Choose IOS so the limits of MSR\_ do not go closer than 2.8V to either  $V_{EE}$  or  $V_{CC}$ . For example, with supplies of +10V and -5V, limit the MSR\_ output to -2.2V and +7.2V. Therefore, set IOS between +1.8V and +3.2V. MSR\_ could clip if IOS is not within this range. Use these general equations for the limits on IOS:

Minimum  $V_{IOS} = V_{EE} + 6.8V$ Maximum  $V_{IOS} = V_{CC} - 6.8V$

### **Current Booster for Highest Current Range**

An external buffer amplifier can be used to provide a current range greater than the MAX9951/MAX9952 maximum ±64mA output current (Figure 5). This function operates as follows:

Figure 5. External Current Boost

### Dual Per-Pin Parametric Measurement Units

A digital output decoded from the range select bits, EXTSEL\_, indicates when to activate the booster. CCOM\_ serves as an input to an external buffer through an internal  $50\Omega$  current-limit series resistor. Connect the external buffer output to the external current-sense resistor, REXT, and to R\_X. Connect the other side of REXT to FORCE\_. Ensure that the external switch is low leakage.

### **Voltage Clamps**

The voltage clamps limit FORCE\_ and operate over the entire specified current range. Set the clamp voltages externally at CLHI\_ and CLLO\_. The voltage at FORCE\_ triggers the clamps independent of the voltage at SENSE\_. When enabled, the clamps function in FI mode only. Use clamp voltages of 0.7V above and below the FORCE\_ voltage range to ensure proper operation of the PMU.

#### **Current Limit**