Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="https://www.onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized applications, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an equif prese

# FAN53540 2.4 MHz, 5 A TinyBuck™ Synchronous Buck Regulator

### Features

- 2.4 MHz Fixed-Frequency Operation

- Best-in-Class Load Transient Response

- 5 A Output Current Capability

- 2.7 V to 5.5 V Input Voltage Range

- Adjustable Output Voltage: 0.8V to 90% of V<sub>IN</sub>

- PFM Mode for High Efficiency in Light Load (Forced PWM Available on MODE Pin)

- 50 µA Typical Quiescent Current in PFM Mode

- External Frequency Synchronization

- Low Ripple Light-Load PFM Mode with Forced PWM Control

- Power Good Output

- Internal Soft-Start

- Input Under-Voltage Lockout (UVLO)

- Thermal Shutdown and Overload Protection

- No External Compensation Required

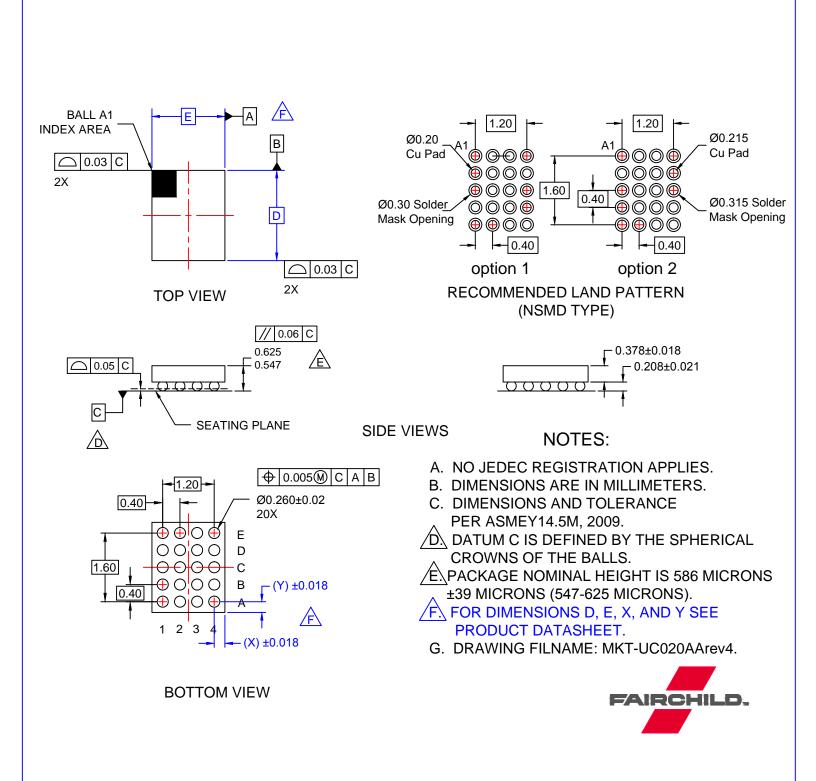

- 20-Bump WLCSP

### Applications

- Set-Top Box

- Hard Disk Drive

- Communications Cards

- DSP Power

### Description

The FAN53540 is a step-down switching voltage regulator that delivers an adjustable output from an input voltage supply of 2.7 V to 5.5 V. Using a proprietary architecture with synchronous rectification, the FAN53540 is capable of delivering 5 A at over 90% efficiency, while maintaining a very high efficiency of over 80% at load currents as low as 2 mA. The regulator operates at a nominal fixed frequency of 2.4 MHz, which reduces the value of the external components to 470 nH for the output inductor and 20  $\mu$ F for the output capacitor. Additional output capacitance can be added to improve regulation during load transients without affecting stability and inductance up to 1.2  $\mu$ H may be used with additional output capacitance.

At moderate and light loads, pulse frequency modulation (PFM) is used to operate the device in power-save mode with a typical quiescent current of 50  $\mu$ A. Even with such a low quiescent current, the part exhibits excellent transient response during large load swings. At higher loads, the system automatically switches to fixed-frequency control, operating at 2.4 MHz. In shutdown mode, the supply current drops below 1  $\mu$ A, reducing power consumption. PFM mode can be disabled if constant frequency is desired. The FAN53540 is available in a 20-bump 1.96 mm x 1.56 mm Wafer-Level Chip-Scale Package (WLCSP).

### **Ordering Information**

| Part Number | Temperature Range | Package                                                                                 | Packing Method |

|-------------|-------------------|-----------------------------------------------------------------------------------------|----------------|

| FAN53540UCX | -4010851.         | 20-Ball Wafer-Level, Chip-Scale Package (WLCSP),<br>4x5 Array, 0.4 mm Pitch, 250µm Ball | Tape and Reel  |

© 2011 Fairchild Semiconductor Corporation FAN53540 • Rev. 1.0.4 FAN53540

I

2.4 MHz, 5 A TinyBuck<sup>™</sup> Synchronous Buck Regulato

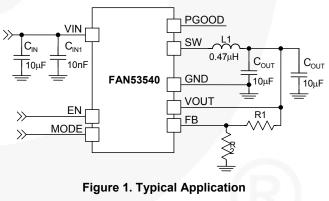

### **Recommended External Components**

| Component        | Description                       | Vendor                  | Parameter | Typical | Unit |

|------------------|-----------------------------------|-------------------------|-----------|---------|------|

| L1               | 470 nH Nominal                    | See Table 2             | L         | 0.47    | μH   |

| Cout             | 10 μF, 6.3 V, X5R, 0805, 2 Pieces | GRM21BR60J106M (Murata) | С         | 10      |      |

| C <sub>IN</sub>  | 10 μF, 6.3 V, X5R, 0805           | C2012X5R0J106M (TDK)    | C         | 10      | μF   |

| C <sub>IN1</sub> | 10 nF, 25 V, X7R, 0402            | Any                     | С         | 10      | nF   |

### Table 1. Recommended External Components for 5 A Maximum Load Current

### Table 2. Recommended Inductors

|                                |                    |        |          |                                   |     | Component Dimensi |     |

|--------------------------------|--------------------|--------|----------|-----------------------------------|-----|-------------------|-----|

| Manufacturer                   | Part#              | L (nH) | DCR (mΩ) | I <sub>MAXDC</sub> <sup>(1)</sup> | L   | W                 | Н   |

| Bourns                         | SRP5012-R47M       | 470    | 19       | 6.0                               | 5.1 | 4.5               | 1.2 |

| Bourns                         | SRP4012-R47M       | 470    | 20       | 5.5                               | 4.6 | 4.0               | 1.2 |

| Coilcraft                      | XPL4020-471ML      | 470    | 19       | 7.2                               | 4.2 | 4.2               | 2.0 |

| Inter-Technical <sup>(2)</sup> | SC2511-R47M        | 470    | 2.6      | 16.0                              | 6.5 | 6.5               | 3.0 |

| TDK                            | VLC5020T-R47M      | 470    | 15       | 5.4                               | 5.0 | 5.0               | 2.0 |

| Vishay                         | IHLP1616ABERR47M01 | 470    | 20       | 5.0                               | 4.5 | 4.1               | 1.2 |

Notes:

1.  $I_{MAXDC}$  is the lesser current to produce  $40^{\circ}$ C temperature rise or 30% inductance roll-off.

2. Inductor used for efficiency and temperature rise measurements.

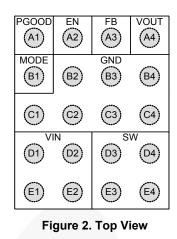

### **Pin Configuration**

(A2) (A3) (A4) (A1) (B4) (B3) **B**2 (B1) (C4) (C3) (C2) (C1) (D4) (D3) (D2) (D1)(E4) (E2) (E3) (E1)

Figure 3. Top View Bottom View

### **Pin Definitions**

| Bump #             | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1                 | PGOOD | Power Good. This open-drain pin pulls LOW if the output falls out of regulation or is in soft-start.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| A2                 | EN    | <b>nable</b> . The device is in Shutdown Mode when this pin is LOW. Do not leave this pin floating. When ing HIGH, use at least a 1 k $\Omega$ series resistor if V <sub>IN</sub> is expected to exceed 4.5 V.                                                                                                                                                                                                             |  |  |  |

| A3                 | FB    | FB. Connect to resistor divider. The IC regulates this pin to 0.8 V.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| A4                 | VOUT  | VOUT. Sense pin for V <sub>OUT</sub> . Connect directly to C <sub>OUT</sub> .                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| B1                 | MODE  | <b>IODE</b> / <b>SYNC</b> . A logic 0 allows the IC to automatically switch to PFM during light loads. When held IGH, the IC to stays in PWM Mode. The regulator also synchronizes its switching frequency to four mes (4X) the frequency provided on this pin ( $f_{MODE}$ ). Do not leave this pin floating. When tying HIGH, se at least a 1 k $\Omega$ series resistor if V <sub>IN</sub> is expected to exceed 4.5 V. |  |  |  |

| B2, B3,<br>C1 – C4 | GND   | <b>Ground</b> . Low-side MOSFET is referenced to this pin. C <sub>IN</sub> and C <sub>OUT</sub> should be returned with a minimal path to these pins.                                                                                                                                                                                                                                                                      |  |  |  |

| B4                 | AGND  | Analog Ground. All signals are referenced to this pin. Avoid routing high dV/dt AC currents through his pin.                                                                                                                                                                                                                                                                                                               |  |  |  |

| D1, D2,<br>E1, E2  | VIN   | Power Input Voltage. Connect to input power source. Connect to C <sub>IN</sub> with minimal path.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| D3, D4,<br>E3, E4  | sw    | Switching Node. Connect to inductor.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter Min. M                                                                          |                                      |      |                    |    |

|------------------|-------------------------------------------------------------------------------------------|--------------------------------------|------|--------------------|----|

|                  | SW, VIN Pins                                                                              |                                      | -0.3 | 7.0 <sup>(3)</sup> |    |

| V <sub>IN</sub>  | Other PinsTied without Series ImpedanceTied through Series Resistance $\geq$ 100 $\Omega$ |                                      | -0.3 | 4.5                | V  |

|                  |                                                                                           |                                      | -0.3 | V <sub>IN</sub>    |    |

| ESD              | Electrostatic Discharge                                                                   | Human Body Model per JESD22-A114     | 22   | 2250               |    |

|                  | Protection Level                                                                          | Charged Device Model per JESD22-C101 | 1500 |                    |    |

| TJ               | Junction Temperature                                                                      |                                      |      | +150               | °C |

| T <sub>STG</sub> | Storage Temperature                                                                       |                                      |      | +150               | °C |

| $T_L$            | Lead Soldering Temperature, 10 Seconds                                                    |                                      |      | +260               | °C |

Note:

3.  $V_{IN}$  slew rate is limited to 1 V/µs.

4. Lesser of 7 V or  $V_{IN}$ +0.3 V.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameter                      | Min. | Тур. | Max.           | Unit |

|------------------|--------------------------------|------|------|----------------|------|

| V <sub>IN</sub>  | Supply Voltage Range           | 2.7  |      | 5.5            | V    |

| V <sub>OUT</sub> | Output Voltage Range           | 0.8  |      | 90% Duty Cycle | V    |

| I <sub>OUT</sub> | Output Current                 | 0    | (    | 5              | А    |

| L                | Inductor                       |      | 0.47 | 1.20           | μH   |

| CIN              | Input Capacitor                |      | 10   |                | μF   |

| Cout             | Output Capacitor               |      | 20   |                | μF   |

| TA               | Operating Ambient Temperature  | -40  |      | +85            | °C   |

| TJ               | Operating Junction Temperature | -40  |      | +125           | °C   |

### **Thermal Properties**

| Symbol          | Parameter                              | Typical           | Unit |

|-----------------|----------------------------------------|-------------------|------|

| θ <sub>JA</sub> | Junction-to-Ambient Thermal Resistance | 38 <sup>(5)</sup> | °C/W |

### Note:

5. See Thermal Considerations in the Applications section.

# FAN53540 — 2.4 MHz, 5 A TinyBuck<sup>™</sup> Synchronous Buck Regulator

### **Electrical Characteristics**

Minimum and maximum values are at  $V_{IN}$ =2.7 V to 5.5 V, and  $T_A$ =-40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$ =25°C,  $V_{IN}$ =5 V, and  $V_{OUT}$ =1.2 V.

| Symbol                                   | Parameter                                                     | Condition                                                                                            | Min.  | Тур.  | Max.  | Unit |

|------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Power Su                                 | ipplies                                                       | ·                                                                                                    |       |       |       |      |

|                                          | Quiescent Current                                             | I <sub>LOAD</sub> =0, MODE=0 (AUTO PFM/PWM)                                                          |       | 50    |       | μA   |

| lq                                       | Quiescent Current                                             | ILOAD=0, MODE=1 (Forced PWM)                                                                         |       | 30    |       | mA   |

| I <sub>SD</sub>                          | Shutdown Supply Current                                       | EN=GND                                                                                               |       | 0.1   | 10.0  | μA   |

| N/                                       |                                                               | V <sub>IN</sub> Rising                                                                               |       | 2.67  | 2.80  | V    |

| V <sub>UVLO</sub>                        | Under-Voltage Lockout Threshold                               | V <sub>IN</sub> Falling                                                                              | 2.1   | 2.3   |       | V    |

| VUVHYST                                  | Under-Voltage Lockout Hysteresis                              |                                                                                                      |       | 365   |       | mV   |

| Logic Pin                                | IS                                                            |                                                                                                      |       |       |       |      |

| VIH                                      | High-Level Input Voltage                                      |                                                                                                      | 1.05  |       |       | V    |

| VIL                                      | Low-Level Input Voltage                                       |                                                                                                      |       |       | 0.4   | V    |

| V <sub>LHYST</sub>                       | Logic Input Hysteresis Voltage                                |                                                                                                      |       | 140   |       | mV   |

| I <sub>IN</sub>                          | Input Bias Current                                            | Input Tied to GND or 1 k $\Omega$ Resistor to VIN                                                    |       | 0.01  | 1.00  | μA   |

| I <sub>OUTL</sub>                        | PGOOD Pull-Down Current                                       | V <sub>PGOOD</sub> =0.4 V                                                                            | 1     |       |       | mA   |

| I <sub>OUTH</sub>                        | PGOOD HIGH Leakage Current                                    | V <sub>PGOOD</sub> =V <sub>IN</sub>                                                                  |       | 0.01  | 1.00  | μA   |

| Vout Reg                                 | ulation                                                       |                                                                                                      |       |       |       |      |

|                                          |                                                               | T <sub>A</sub> =25°C, Forced PWM                                                                     | 0.792 | 0.800 | 0.808 | V    |

| V <sub>REF</sub>                         | Output Reference DC Accuracy,<br>Measured at FB Pin           | T <sub>A</sub> =-40°C to 85°C, Forced PWM                                                            | 0.787 | 0.800 | 0.813 | V    |

|                                          |                                                               | AUTO PFM/PWM                                                                                         | 0.784 | 0.800 | 0.824 | V    |

| $\frac{\Delta V_{OUT}}{\Delta I_{LOAD}}$ | Load Regulation                                               | MODE=V <sub>IN</sub> (Forced PWM)                                                                    |       | -0.02 |       | %//  |

| $rac{\Delta V_{OUT}}{\Delta V_{IN}}$    | Line Regulation                                               | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ I}_{\text{OUT(DC)}}=1.5 \text{ A}$ |       | -0.16 |       | %Λ   |

| I <sub>REF</sub>                         | FB Pin Leakage Current                                        | FB=0.8 V                                                                                             |       | 1     |       | nA   |

| $\Delta V_{OUT}$                         | Transient Response                                            | I <sub>LOAD</sub> Step 0.1 A to 1.5 A, t <sub>R</sub> =100 ns                                        |       | -30   |       | m۷   |

| Power Sv                                 | vitch and Protection                                          |                                                                                                      | C     |       |       |      |

| R <sub>DS(ON)P</sub>                     | P-Channel MOSFET On Resistance                                |                                                                                                      |       | 33    | 1     | mΩ   |

| R <sub>DS(ON)N</sub>                     | N-Channel MOSFET On Resistance                                |                                                                                                      |       | 28    |       | mΩ   |

|                                          |                                                               | Open Loop                                                                                            | 5.8   | 7.5   | 8.8   | Α    |

| ILIMPK                                   | P-MOS Peak Current Limit                                      | Closed Loop                                                                                          |       | 8     |       | Α    |

| TLIMIT                                   | Thermal Shutdown                                              |                                                                                                      |       | 155   |       | °C   |

| T <sub>HYST</sub>                        | Thermal Shutdown Hysteresis                                   |                                                                                                      |       | 20    |       | °C   |

| .,                                       |                                                               | Rising Threshold                                                                                     |       | 6.1   |       | V    |

| V <sub>SDWN</sub>                        | Input OVP Shutdown                                            | Falling Threshold                                                                                    | 5.5   | 5.8   |       | V    |

| Frequenc                                 | y Control                                                     | •                                                                                                    |       |       |       |      |

| f <sub>SW</sub>                          | Oscillator Frequency                                          |                                                                                                      | 2.1   | 2.4   | 3.0   | MH   |

| <b>f</b> <sub>MODE</sub>                 | MODE Pin Synchronization Range                                | External Square-Wave, 30% to 70% Duty Cycle                                                          | 525   | 600   | 700   | kHz  |

| Soft-Star                                | t and Output Discharge                                        | •                                                                                                    |       |       | •     |      |

| t <sub>ss</sub>                          | Regulator Enable to Regulated V <sub>OUT</sub> (Rising PGOOD) |                                                                                                      |       | 1.2   |       | ms   |

| R <sub>DIS</sub>                         | Output Discharge Resistance                                   | EN=0 V                                                                                               |       | 175   |       | Ω    |

FAN53540 ---

5000

5.5

5000

7

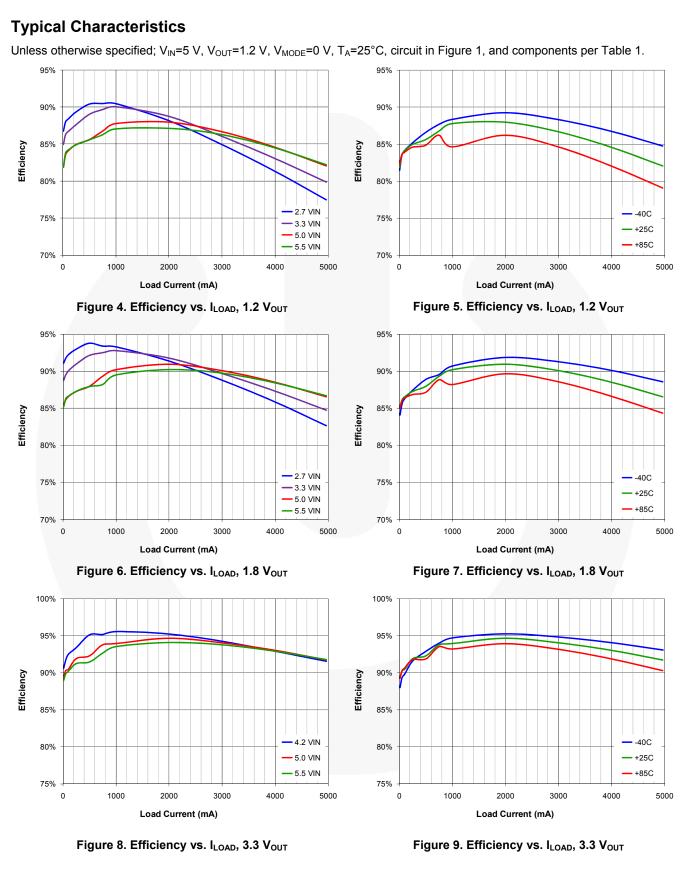

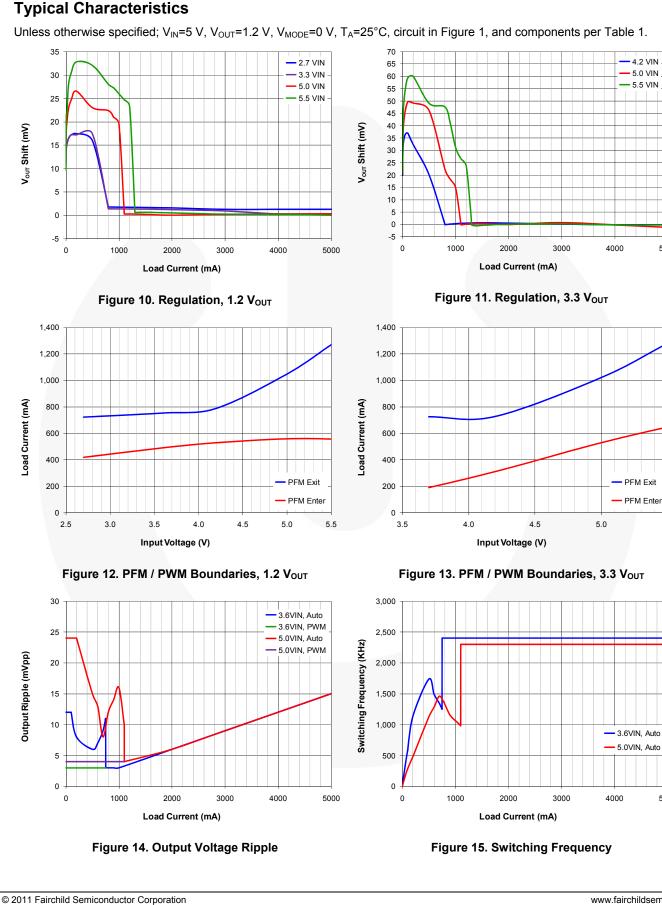

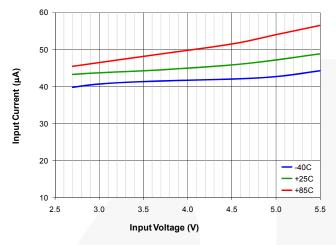

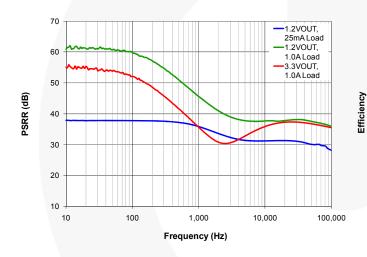

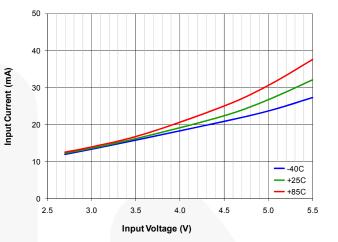

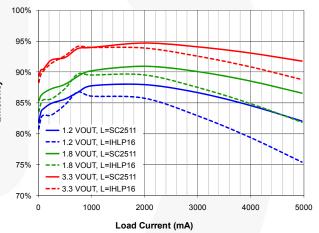

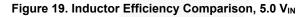

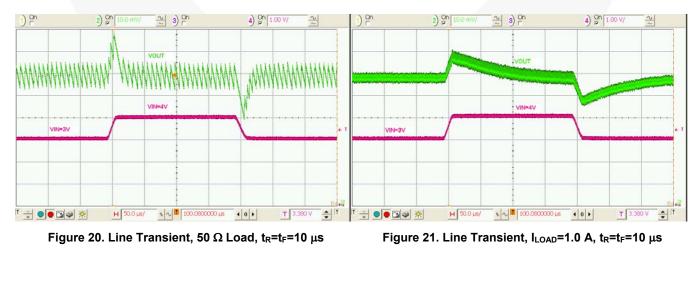

### **Typical Characteristics**

Unless otherwise specified; V<sub>IN</sub>=5 V, V<sub>OUT</sub>=1.2 V, V<sub>MODE</sub>=0 V, T<sub>A</sub>=25°C, circuit in Figure 1, and components per Table 1.

Figure 18. Power Supply Rejection (PSRR)

Figure 17. Quiescent Current, PMW Mode, EN=VIN

### **Operation Description**

The FAN53540 is a step-down switching voltage regulator that delivers an adjustable output from an input voltage supply of 2.7 V to 5.5 V. Using a proprietary architecture with synchronous rectification, the FAN53540 is capable of delivering up to 5 A at over 90% efficiency. The regulator operates at a nominal frequency of 2.4 MHz at full load, which reduces the value of the external components to 470 nH for the output inductor and 20  $\mu$ F for the output capacitor. High efficiency is maintained at light load with single-pulse PFM Mode.

### **Control Scheme**

The FAN53540 uses a proprietary non-linear, fixedfrequency PWM modulator to deliver very fast load transient response, while maintaining a constant switching frequency over a wide range of operating conditions.

Regulator performance is independent of the output capacitor ESR, allowing for the use of ceramic output capacitors. Although this type of operation normally results in a switching frequency that varies with input voltage and load current, an internal frequency loop holds the switching frequency constant over a large range of input voltages and load currents.

For very light loads, the FAN53540 operates in Discontinuous Current (DCM) single-pulse PFM Mode, which produces low output ripple compared with other PFM architectures. Transition between PWM and PFM is seamless, with a glitch of less than 3% of  $V_{OUT}$  during the transition between DCM and CCM Modes.

PFM Mode is disabled by holding the MODE pin HIGH. The IC synchronizes to the MODE pin frequency. When synchronizing to the MODE pin, PFM Mode is disabled.

### **Setting Output Voltage**

The output voltage is set by the R1, R2, and  $V_{REF}$  (0.8 V):

$$\frac{R1}{R2} = \frac{V_{OUT} - V_{REF}}{V_{REF}}$$

(1)

R1 must be set at or below 100 k $\Omega$ ; therefore:

$$R2 = \frac{R1 \cdot 0.8}{(V_{OUT} - 0.8)}$$

(2)

For example, for V<sub>OUT</sub>=1.2 V, R1=100 k $\Omega$ , R2=200 k $\Omega$ .

### **Enable and Soft-Start**

When the EN pin is LOW, the IC is shut down, all internal circuits are off, and the part draws very little current. Raising EN above its threshold voltage activates the part and starts the soft-start cycle. During soft-start, the modulator's internal reference is ramped slowly to minimize surge currents on the input and prevents overshoot of the output voltage.

If large values of output capacitance are used, the regulator may fail to start. If  $V_{OUT}$  fails to achieve regulation within 1.2 ms from the beginning of soft-start, the regulator shuts down and waits 1.6 ms before attempting a restart. If the regulator is in current limit for 16 consecutive PWM cycles, the regulator shuts down before restarting 1.6 ms later. This

limits the  $C_{\text{OUT}}$  capacitance when a heavy load (  $I_{\text{LOAD}(\text{SS})}$  ) is applied during the startup.

The maximum  $C_{\text{OUT}}$  capacitance for successful starting with a heavy constant-current load is approximately:

$$C_{OUT_{MAX}} \approx (5.8 - I_{LOAD}) \bullet \frac{800}{V_{OUT}}$$

(3)

where  $C_{OUTMAX}$  is expressed in  $\mu F$  and  $I_{LOAD}$  is the load current during soft-start, expressed in A.

Diode Emulation Mode is employed during soft-start, allowing the IC to start into a pre-charged output. Diode emulation prohibits reverse inductor current from flowing through the synchronous rectifier.

When EN is LOW, a 150  $\Omega$  resistor discharges V<sub>OUT</sub>.

### **Under-Voltage Lockout (UVLO)**

When EN is HIGH, the under-voltage lockout keeps the part from operating until the input supply voltage rises high enough to operate properly. This ensures no misbehavior of the regulator during startup or shutdown.

### Input Over-Voltage Protection (OVP)

When  $V_{IN}$  exceeds  $V_{SDWN}$  (about 6.1 V), the IC stops switching to protect the circuitry from excessive internal voltage spikes. An internal filter prevents the circuit from shutting down due to  $V_{IN}$  noise spikes.

### **Current Limiting**

A heavy load or short circuit on the output causes the current in the inductor to increase until a maximum current threshold is reached in the high-side switch. Upon reaching this point, the high-side switch turns off, preventing high currents from causing damage. 16 consecutive PWM cycles in current limit cause the regulator to shut down and stay off for about 1.6 ms before attempting a restart.

In the event of a short circuit, the soft-start circuit attempts to restart and produces an over-current fault after 16 consecutive cycles in current limit, which results in a duty cycle of less than 5%, providing current into a short circuit.

### **External Frequency Synchronization**

Logic 1 on the MODE pin forces the IC to stay in PWM Mode. Logic 0 allows the IC to automatically switch to PFM during light loads. If the MODE pin is toggled, the converter synchronizes its switching frequency to four times the frequency on the mode pin ( $f_{MODE}$ ).

The MODE pin is internally buffered with a Schmitt trigger, which allows the MODE pin to be driven with slow rise and fall times. An asymmetric duty cycle for frequency synchronization is permitted, provided it is consistent with parametric table limits.

### **PGOOD** Pin

The PGOOD pin is an open-drain that indicates that the IC is in regulation when its state is open. PGOOD pulls LOW under the following conditions:

- The IC has operated in cycle-by-cycle current limit for eight consecutive PWM cycles;

- The circuit is disabled, either after a fault occurs or when EN is LOW; or

- The IC is performing a soft-start.

### **Thermal Shutdown**

When the die temperature increases, due to a high load condition and/or a high ambient temperature, the output switching is disabled until the temperature on the die has fallen sufficiently. The junction temperature at which the thermal shutdown activates is nominally 155°C with a 20°C hysteresis.

### Minimum Off-Time Effect on Switching Frequency

$t_{OFF(MIN)}$  is 45 ns, which constrains the maximum  $V_{OUT}/V_{IN}$  that the FAN53540 can provide, while still maintaining a fixed switching frequency in PWM Mode. Regulation is maintained even though the regulator is unable to provide sufficient duty-cycle and operate at 2.4 MHz.

Switching frequency is the lower of 2.4 MHz or:

$$f_{SW}(MHz) = 22.2 \bullet \left( 1 - \frac{V_{OUT} + I_{OUT} \bullet R_{OFF}}{V_{IN} + I_{OUT} \bullet (R_{OFF} - R_{ON})} \right)$$

(4)

where:

I<sub>OUT</sub> = load current, in A;

$R_{ON} = R_{DS(ON)_P} + DCR_L$ , in Ohms; and

$R_{OFF} = R_{DS(ON)_N} + DCR_L$ , in Ohms.

A result of <0 MHz indicates 100% duty cycle operation.

### **Application Information**

### Selecting the Inductor

The output inductor must meet both the required inductance and the energy handling capability of the application. The inductor value affects the average current limit, output voltage ripple, transient response, and efficiency.

The ripple current ( $\Delta I$ ) of the regulator is:

$$\Delta I \approx \frac{V_{OUT}}{V_{IN}} \bullet \left( \frac{V_{IN} - V_{OUT}}{L \bullet f_{SW}} \right)$$

(5)

The maximum average load current,  $I_{MAX(LOAD)}$ , is related to the peak current limit,  $I_{LIM(PK)}$ , by the ripple current as:

$$I_{MAX(LOAD)} = I_{LIM(PK)} - \frac{\Delta I}{2}$$

(6)

The FAN53540 is optimized for operation with L=470 nH, but is stable with inductances up to 1.2  $\mu H$  (nominal). The inductor should be rated to maintain at least 80% of its value at I\_{LIM(PK)}. Failure to do so lowers the amount of DC current the IC can deliver.

Efficiency is affected by the inductor DCR and inductance value. Decreasing the inductor value for a given physical size typically decreases the DCR; but since  $\Delta I$  increases, the RMS current increases, as do core and skin-effect losses.

$$RMS = \sqrt{I_{OUT(DC)}^{2} + \frac{\Delta I^{2}}{12}}$$

(7)

The increased RMS current produces higher losses through the  $R_{DS(ON)}$  of the IC MOSFETs as well as the inductor ESR.

Increasing the inductor value produces lower RMS currents, but degrades transient response. For a given physical inductor size, increased inductance usually results in an inductor with lower saturation current.

Table 3 shows the effects on regulator performance of higher inductance than the recommended 470 nH.

# Table 3. Inductor Value and RegulatorPerformance

| I <sub>MAX(LOAD)</sub> | $\Delta \mathbf{V}_{OUT}$ (EQ. 8) | Transient Response |

|------------------------|-----------------------------------|--------------------|

| Increase               | Decrease                          | Degraded           |

### Inductor Current Rating

The FAN53540's current-limit circuit can allow a peak current of about 8.8 A to flow through L1 under worst-case conditions. If it is possible for the load to draw that much continuous current, the inductor should be capable of sustaining that current or failing in a safe manner.

For space-constrained applications, a lower current rating for L1 can be used. The FAN53540 may still protect these inductors in the event of a short circuit, but may not be able to protect the inductor from failure if the load is able to draw higher currents than the DC rating of the inductor.

L

### Output Capacitor and VOUT Ripple

Table 1 suggests 0805 capacitors, but 0603 capacitors may be used if space is at a premium. Due to voltage effects, the 0603 capacitors have a lower in-circuit capacitance, which can degrade transient response and output ripple.

Increasing  $C_{\text{OUT}}$  has a negligible effect on loop stability and can be increased to reduce output voltage ripple or to improve transient response. Output voltage ripple,  $\Delta V_{\text{OUT}}$ , is:

$$\Delta V_{OUT} = \Delta I \bullet \left( \frac{1}{8 \bullet C_{OUT} \bullet f_{SW}} + ESR \right)$$

(8)

where  $C_{\text{OUT}}$  is the effective output capacitance. The capacitance of  $C_{\text{OUT}}$  decreases at higher output voltages, which results in higher  $\Delta V_{\text{OUT}}$ . If large values are used for  $C_{\text{OUT}}$ , the regulator may fail to start under load. If an inductor value greater than 1.0  $\mu\text{H}$  is used, at least 30  $\mu\text{F}$  of  $C_{\text{OUT}}$  should be used to ensure transient response performance.

The lowest  $\Delta V_{OUT}$  is obtained when the IC is in PWM Mode and, therefore, operating at 2.4 MHz. In PFM Mode,  $f_{SW}$  is reduced, causing  $\Delta V_{OUT}$  to increase.

### **ESL Effects**

The Equivalent Series Inductance (ESL) of the output capacitor network should be kept low to minimize the squarewave component of output ripple that results from the division ratio  $C_{OUT}$  ESL and the output inductor ( $L_{OUT}$ ). The squarewave component due to the ESL can be estimated as:

$$\Delta V_{OUT(SQ)} \approx V_{IN} \bullet \frac{ESL_{COUT}}{L1}$$

(9)

A good practice to minimize this ripple is to use multiple output capacitors to achieve the desired  $C_{OUT}$  value. For example, to obtain  $C_{OUT}$ =20  $\mu$ F, a single 22  $\mu$ F 0805 would produce twice the square wave ripple of two 10  $\mu$ F 0805.

To minimize ESL, try to use capacitors with the lowest ratio of length to width. 0805s have lower ESL than 1206 s. If very low output ripple is necessary, research vendors that produce 0508 or 0612 capacitors with ultra-low ESL. Placing additional small value capacitors near the load also reduces the high-frequency ripple components.

### **Input Capacitor**

The 10  $\mu$ F ceramic input capacitor should be placed as close as possible between the VIN pin and PGND to minimize the parasitic inductance. If a long wire is used to bring power to the IC, additional "bulk" capacitance (electrolytic or tantalum) should be placed between C<sub>IN</sub> and the power source lead to reduce under-damped ringing that can occur between the inductance of the power source leads and C<sub>IN</sub>.

The effective  $C_{IN}$  capacitance value decreases as  $V_{IN}$  increases due to DC bias effects. This has no significant impact on regulator performance.

To reduce ringing and overshoot on VIN and SW, an additional bypass capacitor  $C_{IN1}$  is recommended. Because this lower value capacitor has a higher resonant frequency than  $C_{IN}$ ;  $C_{IN1}$  should be placed closer to the VIN and GND pins of the IC than  $C_{IN}$ .

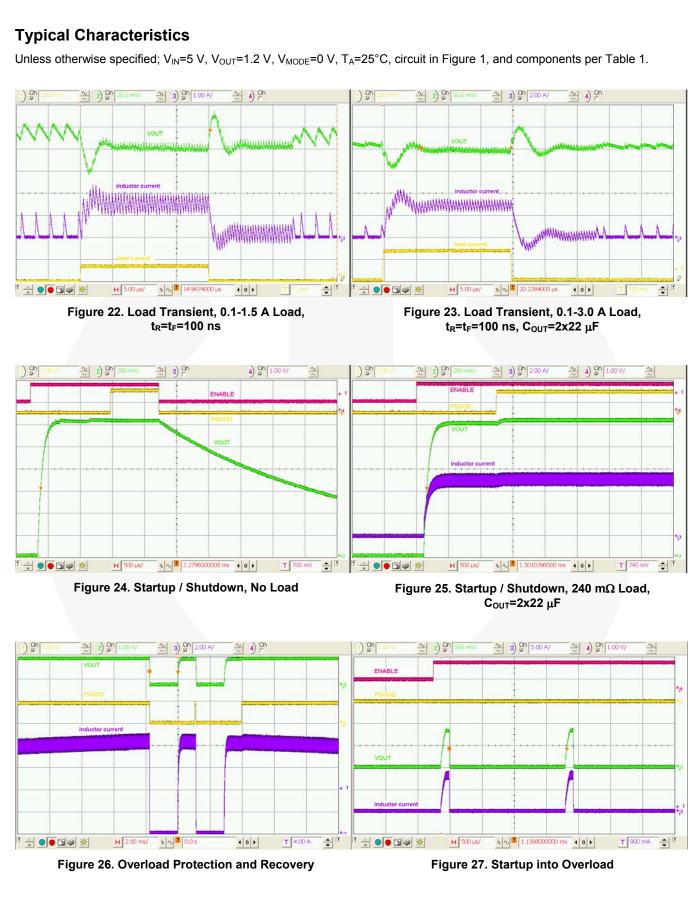

### Layout Recommendations

The layout example below illustrates the recommended component placement and top copper (green) routing. The inductor in this example is the TDK VLC5020T-R47N.

To minimize VIN and SW spikes and thereby reduce voltage stress on the IC's power switches, it is critical to minimize the loop length for the VIN bypass capacitors.

Switching current paths through  $C_{IN}$  and  $C_{OUT}$  should be returned directly to the GND bumps of the IC on the top layer of the printed circuit board (PCB). VOUT and GND connections to the system power and ground planes can be made through multiple vias placed as close as possible to the  $C_{OUT}$  capacitors. The regulator should be placed as close to its load as possible to minimize trace inductance and capacitance.

Figure 28. Recommended Layout

Connect the VOUT pin and R1 directly to  $C_{OUT}$  using a low impedance path (shown in red in Figure 28. Recommended Layout). A  $\geq$ 0.4 mm wide trace is recommended. Avoid routing this trace directly beneath SW unless separated by an internal GND plane.

If the MODE function is not required, extend the ground plane through the MODE pin to reduce the loop inductance for the VIN bypass.

### **Thermal Considerations**

Heat is removed from the IC through the solder bumps to the PCB copper. The junction-to-ambient thermal resistance  $(\theta_{JA})$  is largely a function of the PCB layout (size, copper weight, and trace width) and the temperature rise from junction to ambient ( $\Delta$ T).

For the FAN53540UC,  $\theta_{JA}$  is 38°C/W when mounted on its four-layer evaluation board in still air, with 2 oz. outer layer copper weight and 1 oz. inner layers. Halving the copper thickness results in an increased  $\theta_{JA}$  of 48°C/W.

For long term reliable operation, the IC's junction temperature (T\_J) should be maintained below 125°C.

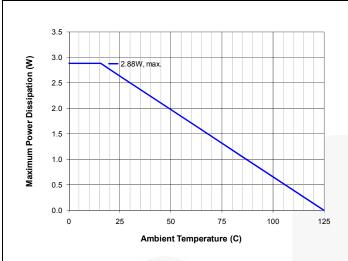

Maximum IC power loss is 2.88 W. Figure 29 shows required power dissipation and derating for a FAN53540UC mounted on the Fairchild evaluation board in still air (38°C/W).

Figure 29. Power Derating

To calculate maximum operating temperature ( $\leq$ 125°C) for a specific application:

- 1. Use efficiency graphs to determine efficiency for the desired  $V_{IN}$ ,  $V_{OUT}$ , and load condition

- 2. Calculate IC power dissipation using:

$$\mathbf{P}_{\rm IC} = \mathbf{V}_{\rm OUT} \bullet \mathbf{I}_{\rm LOAD} \bullet \left(\frac{1}{\eta} - 1\right) \tag{10}$$

where  $\eta$  is efficiency from Figure 4 through Figure 9.

3. Compute inductor copper losses using:

$$P_{L} = I_{LOAD}^{2} \bullet DCR_{L}$$

(11)

4. Combine IC (step 2) and inductor losses (step 3) to determine total dissipation:

$$\mathsf{P}_{\mathsf{D}} = \mathsf{P}_{\mathsf{IC}} + \mathsf{P}_{\mathsf{L}} \tag{12}$$

5. Determine device operating temperature:

$$\Delta T = P_D \bullet R_{\theta JA} \text{ and } T_{IC} = T_{AMB} + \Delta T$$

(13)

Device temperature (T<sub>IC</sub>) should not exceed 125°C.

A different approach, shown here as an example, uses the same equations to determine maximum inductor DCR for a specific application:

If a design requires a 5.0V  $_{I\!N},\,1.2$   $V_{OUT},\,4$   $A_{RMS},\,at$  75°C:

- A. From Figure 4,  $\eta$  is ~82%.

- B. From Eq. 10, P<sub>IC</sub>=1,054 mW.

- C. From Eq. 13, maximum  $P_D=1,316$  mW for 50°C rise.

- D. From Eq. 12,  $P_L$ =262 mW.

- E. From Eq. 11, DCR<16.4 m $\Omega$ .

Due to the +0.4%°C temperature coefficient of copper, inductor DCR must be further reduced to accommodate the  $\sim$ 50°C temperature rise.

To meet the design requirements, an inductor with a room temperature DCR of <13.6 m $\Omega$  is necessary.

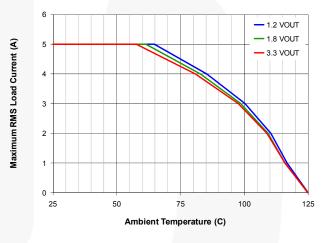

Figure 30 shows the maximum ambient temperature where FAN53540UC can be used for a continuous load, at 5.0  $V_{IN}$ :

### Figure 30. Load Current Derating<sup>(6)</sup>

### Note:

6. The graph was empirically determined using an ultra-low DCR (2.6 m $\Omega$ ) inductor. For physically smaller devices with higher DCR, further derating may be necessary.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC