## Product Specification PE4305

## **Product Description**

The PE4305 is a high linearity, 5-bit RF Digital Step Attenuator (DSA) covering a 15.5 dB attenuation range in 0.5 dB steps, and is pin compatible with the PE430x series. This 50-ohm RF DSA provides both parallel (latched or direct mode) and serial CMOS control interface, operates on a single 3-volt supply and maintains high attenuation accuracy over frequency and temperature. It also has a unique control interface that allows the user to select an initial attenuation state at power-up. The PE4305 exhibits very low insertion loss and low power consumption. This functionality is delivered in a 4x4 mm QFN footprint.

The PE4305 is manufactured on Peregrine's UltraCMOS<sup>™</sup> process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate, offering the performance of GaAs with the economy and integration of conventional CMOS.

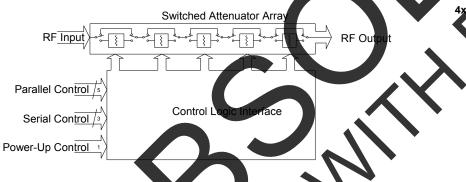

#### Figure 1. Functional Schematic Diagram

## 50 Ω RF Digital Attenuator 5-bit, 15.5 dB, DC – 4.0 GHz

#### Features

- Attenuation: 0.5 dB steps to 15.5 dB

- Flexible parallel and serial programming interfaces

- Latched or direct mode

- Unique power-up state selection

- Positive CMOS control log

- High attenuation accuracy and linearity

over temperature and frequency

- Very low power consumption

- Single-supply operation

- 50 Ω impedance

- Pin compatible with PE430x series

ackage Type

Packaged in a 20 Lead 4x4 mm QFN

## Table 1. Electrical Specifications @ +25°C, V<sub>DD</sub> = 3.0 V

| Parameter                     | Test Conditions                      | Frequency       | Minimum | Typical | Maximum                                                                          | Units |

|-------------------------------|--------------------------------------|-----------------|---------|---------|----------------------------------------------------------------------------------|-------|

| Operation Frequency           |                                      |                 | DC      |         | 4000                                                                             | MHz   |

| Insertion Loss <sup>2</sup>   |                                      | DC - 2.2 GHz    | -       | 1.5     | 2.25                                                                             | dB    |

| Attenuation Accuracy          | Any Bit or Bit<br>Combination        | DC - 2.2 GHz    | -       | -       | $\pm(0.25 + 3\% \text{ of atten setting})$<br>not to exceed $\pm 0.4 \text{ dB}$ | dB    |

| 1 dB Compression <sup>3</sup> |                                      | 1 MHz - 2.2 GHz | 30      | 34      | -                                                                                | dBm   |

| Input IP3 <sup>1, 2</sup>     | Two-tone inputs<br>+18 dBm           | 1 MHz - 2.2 GHz | -       | 52      | -                                                                                | dBm   |

| Return Loss                   |                                      | DC - 2.2 GHz    | 15      | 20      | -                                                                                | dB    |

| Switching Speed               | 50% control to 0.5 dB of final value |                 | -       | -       | 1                                                                                | μS    |

Notes: 1. Device Linearity will begin to degrade below 1Mhz

See Maximput rating in Table 3 & Figures on Pages 2 to 4 for data across frequency.

3. Note Absolute Maximum in Table 3.

Document No. 70-0159-06 | www.psemi.com

### Typical Performance Data @ 25°C, V<sub>DD</sub> = 3.0 V

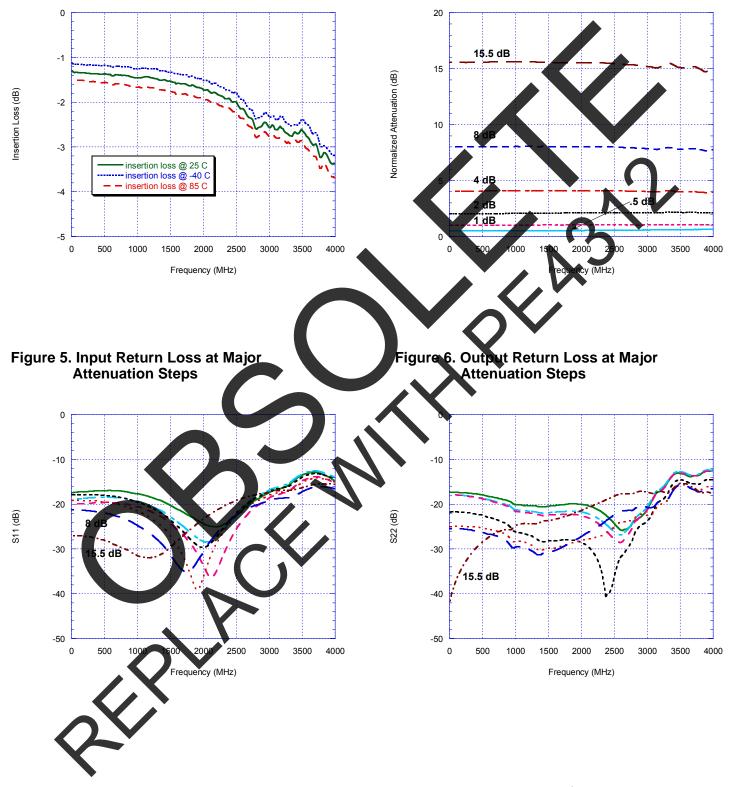

## Figure 3. Insertion Loss

Figure 4. Attenuation at Major steps

## Typical Performance Data @ $25^{\circ}$ C, V<sub>DD</sub> = 3.0 V

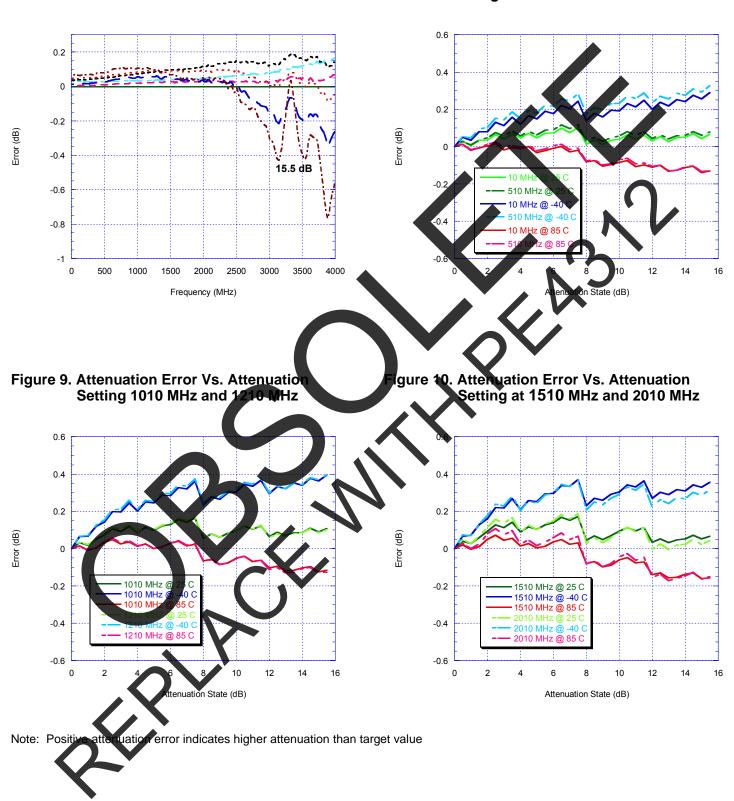

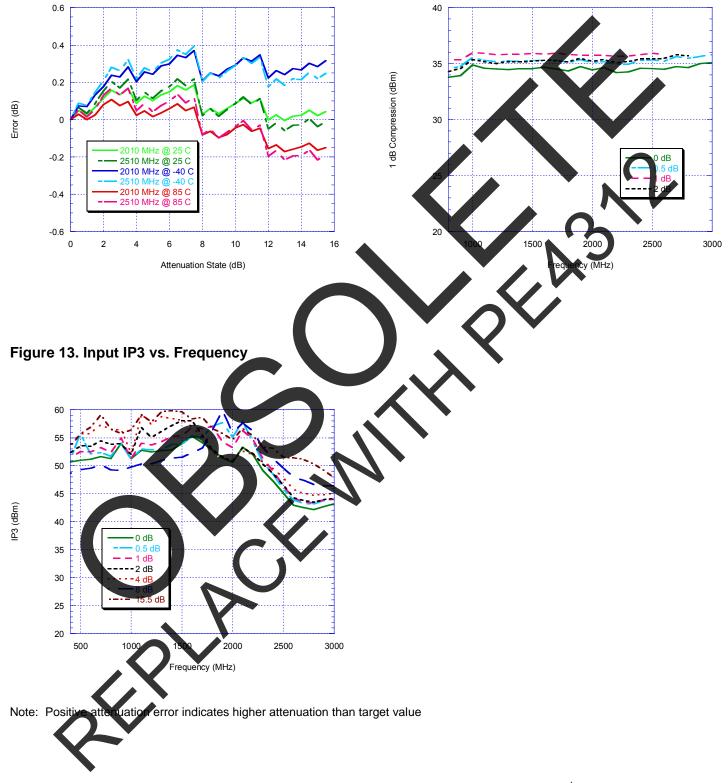

Figure 7. Attenuation Error Vs. Frequency

Figure 8. Attenuation Error Vs. Attenuation Setting at 10 MHz and 510 MHz

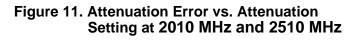

## Typical Performance Data @ 25°C, V<sub>DD</sub> = 3.0 V

Figure 12. 1 dB Compression vs. Frequency

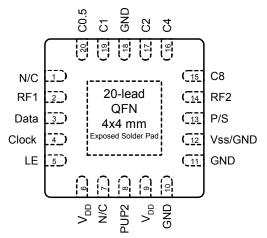

## Figure 14. Pin Configuration (Top View)

#### Table 2. Pin Descriptions

| Pin No. | Pin Name             | Description                                          |

|---------|----------------------|------------------------------------------------------|

| 1       | N/C                  | No connect. Can be connected to any bias.            |

| 2       | RF1                  | RF port (Note 1).                                    |

| 3       | Data                 | Serial interface data input (Note 4).                |

| 4       | Clock                | Serial interface clock input.                        |

| 5       | LE                   | Latch Enable input (Note 2).                         |

| 6       | V <sub>DD</sub>      | Power supply pin.                                    |

| 7       | N/C                  | No connect. Can be connected to any bias.            |

| 8       | PUP2                 | Power-up selection bit.                              |

| 9       | V <sub>DD</sub>      | Power supply pin.                                    |

| 10      | GND                  | Ground connection.                                   |

| 11      | GND                  | Ground connection.                                   |

| 12      | V <sub>ss</sub> /GND | Negative supply voltage or GND<br>connection(Note 3) |

| 13      | P/S                  | Parallel/Serial mode select.                         |

| 14      | RF2                  | RF port (Note 1).                                    |

| 15      | 28                   | Attenuation control bit, 8 dB.                       |

| 16      | C4                   | Attenuation control bit, 4 dB                        |

| 17      | C2                   | Attenuation control bit, 2 dB.                       |

| 18      | GND                  | Ground connection.                                   |

| 19      | C1                   | Attenuation control bit, 1 dB.                       |

| 20      | C0.5                 | Attenuation control bit, 0.5 dB.                     |

| Paddle  | GND                  | Ground for proper operation                          |

Note 1: Both RF ports must be held at 0 VDC or DC blocked with an external series capacitor.

2: Latch Enable (LE) has an internal 100  $k\Omega$  resistor to VDD.

3: Connect pin 12 to GND to enable internal negative voltage generator. Connect pin 12 to VSS (-VDD) to bypass and disable internal negative voltage generator.

4. Place 10 kC resistor in series, as close to pin as possible to avoid frequency resonance. See "Resistor on Pin 3" paragraph.

Document No. 70-0159-06 | www.psemi.com

#### Table 3. Absolute Maximum Ratings

| Symbol           | Parameter/Conditions              | Min  | Max                      | Units |

|------------------|-----------------------------------|------|--------------------------|-------|

| V <sub>DD</sub>  | Power supply voltage              | -0.3 | 4.0                      | V     |

| Vı               | Voltage on any DC input           | -0.3 | V <sub>DD</sub> +<br>0.3 | V     |

| T <sub>ST</sub>  | Storage temperature range         | -65  | 150                      | °C    |

| P <sub>IN</sub>  | Input power (50Ω)                 |      | +30                      | dBm   |

| V <sub>ESD</sub> | ESD voltage (Human Body<br>Model) |      | 500                      | V     |

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

## Table 4. Operating Ranges

| Min                 | Тур            | Max                             | Units                                                 |

|---------------------|----------------|---------------------------------|-------------------------------------------------------|

| 2.7                 | 20             | 3.3                             | V                                                     |

|                     |                | 100                             | μA                                                    |

| 0.7xV <sub>DD</sub> |                |                                 | V                                                     |

|                     |                | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V                                                     |

|                     |                | 1                               | μA                                                    |

|                     |                | +24                             | dBm                                                   |

| -40                 |                | 85                              | °C                                                    |

|                     | 2.7<br>07x VDD |                                 | 2.7 3.3<br>100<br>007xVpp<br>0.3xVpp<br>1<br>1<br>+24 |

#### Exposed Solder Pad Connection

The exposed solder pad on the bottom of the package must be grounded for proper device operation.

#### Electrostatic Discharge (ESD) Precautions

When handling this UltraCMOS<sup>™</sup> device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rate specified in Table 3.

#### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS<sup>™</sup> devices are immune to latch-up.

#### **Switching Frequency**

The PE4305 has a maximum 25 kHz switching rate.

#### **Resistor on Pin 3**

A 10 k $\Omega$  resistor on the input to Pin 3 (see Figure 16) will eliminate package resonance between the RF input pin and the digital input. Specified attenuation error versus frequency performance is dependent upon this condition.

#### **Programming Options**

#### Parallel/Serial Selection

Either a parallel or serial interface can be used to control the PE4305. The P/S bit provides this selection, with P/S=LOW selecting the parallel interface and P/S=HIGH selecting the serial interface.

#### Parallel / Direct Mode Interface

The parallel interface consists of five CMOScompatible control lines that select the desired attenuation state, as shown in Table 5.

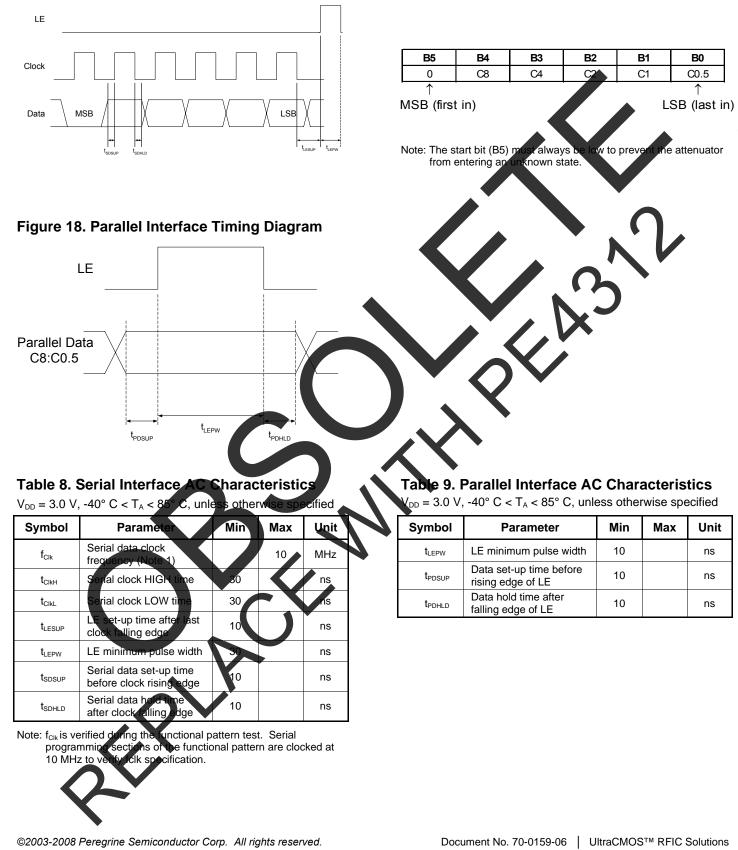

The parallel interface timing requirements are defined by Figure 18 (Parallel Interface Timing Diagram), Table 9 (Parallel Interface AC Characteristics), and switching speed (Table 1).

For parallel programming the Latch Enable (LE) should be held LOW while changing attenuation state control values, then pulse LE HIGH to LOW (per Figure 18) to latch new attenuation state into device.

For direct programming, the Latch Enable (LE) line should be pulled HIGH. Changing attenuation state control values will change device state to new attenuation. Direct Mode is ideal for manual control of the device (using hardwire, switches, or jumpers).

#### Table 5. Truth Table

| P/S | C8 | C4 | C2 | C1 | C0.5 | Attenuation<br>State |

|-----|----|----|----|----|------|----------------------|

| 0   | 0  | 0  | 0  | 0  | 0    | Reference Loss       |

| 0   | 0  | 0  | 0  | 0  | 1    | 0 S dB               |

| 0   | 0  | 0  | 0  | 1  |      | 1 dB                 |

| 0   | 0  | 0  | 1  | 0  | 0    | 2 dB                 |

| 0   | 0  | 1  | 0  | 9  | 0    | 4 dB                 |

| 0   | 1  | 0  | 0  | 0  | 0    | 8 dB                 |

| 0   | 1  | 1  | 1  | 1  | 1    | 15.5 dB              |

Note: Not all 32 possible combinations of CV 5-C8 are shown in table

#### Serial Interface

The PE4305's serial interface is a 6-bit serial-in, parallel-out shift register buffered by a transparent latch. The latch is controlled by three CMOScompatible signals. Data, Clock, and Latch Enable (LE). The Data and Clock inputs allow data to be

©2003-2008 Peregrine Semiconductor Corp. All rights reserved.

serially entered into the shift register, a process that is independent of the state of the LE input.

The LE input controls the latch. When LE is HIGH, the latch is transparent and the contents of the serial shift register control the attenuator. When LE is brought LOW, data in the shift register is latched.

The shift register should be loaded while LE is held LOW to prevent the attenuator value from changing as data is entered. The LE input should then be toggled HIGH and brought LOW again, tatching the new data. The star bit (B5) of the data should always be low to prevent an unknown state in the device. The timing for this operation is defined by Figure 17 (Serial Interface Timing Diagram) and Table 8 (Serial Interface AC Characteristics).

#### Power-up Control Settings

The PE4305 always assumes a specifiable attenuation setting on power-up. This feature exists for both the Serial and Paratel modes of operation, and allows a known attenuation state to be established before an initial serial or parallel control word is provided.

When the attenuator powers up in Serial mode (P/S=1), the five control bits are set to whatever data is present on the five parallel data inputs (C0.5 to C8). This shows any one of the 32 attenuation settings to be specified as the power-up state.

When the attenuator powers up in Parallel mode (P/ =0) with LE=0, the control bits are automatically set to one of two possible values. These two values are selected by the power-up control bit, PUP2, as shown in Table 6 (Power-Up Truth Table, Parallel Mode).

## Table 6. Power-Up Truth Table, ParallelInterface Mode

| P/S | LE | PUP2 | Attenuation State  |

|-----|----|------|--------------------|

| 0   | 0  | 0    | Reference Loss     |

| 0   | 0  | 1    | 8 dB               |

| 0   | 1  | Х    | Defined by C0.5-C8 |

Note: Power up with LE=1 provides normal parallel operation with C0.5-C8, and PUP2 is not active

## **Evaluation Kit**

The Digital Attenuator Evaluation Kit board was designed to ease customer evaluation of the PE4305 DSA.

J9 is used in conjunction with the supplied DC cable to supply VDD, GND, and –VDD. If use of the internal negative voltage generator is desired, then connect –VDD (black banana plug) to ground. If an external –VDD is desired, then apply -3V.

J1 should be connected to the LPT1 port of a PC with the supplied control cable. The evaluation software is written to operate the DSA in serial mode, so switch 7 (P/S) on the DIP switch SW1 should be ON with all other switches off. Using the software, enable or disable each attenuation setting to the desired combined attenuation. The software automatically programs the DSA each time an attenuation state is enabled or disabled.

To evaluate the Power Up options, first disconnect the control cable from the evaluation board. The control cable must be removed to prevent the PC port from biasing the control pins.

During power up with P/S=1 high and LE=0 or P/S=0 low and LE=1, the default power-up signal attenuation is set to the value present on the five control bits on the five parallel data inputs (C0.5 to C8). This allows any one of the 32 attenuation settings to be specified as the power-up state.

During power up with P/S=0 high and LE=0, the control bits are automatically set to one of two possible values presented through the PUP interface. These two values are selected by the power-up control bit, PUP2, as showin in Table 6. Pins 1 and 7 are open and may be connected to any bias.

## **Resistor on Pin 3**

A 10 k $\Omega$  resistor on the input to bin 3 (Figure 16) will eliminate package resonance between the RF input pin and the digital input. Specified attenuation error versus frequency performance is dependent upon this condition.

Document No. 70-0159-06 | www.psemi.com

#### Figure 15. Evaluation Board Layout

Peregrine Specification 101/0112

Figure 16. Evaluation Board Schematic Reregrine Specification 102/0144

30 CF 3 5 GND RFin RFout U1 QFN4X4 DATA DATA PS **VPS** SMA 10 kohr SMA 4 12 CLK CLK VNEG 11 PUP2 I F G∰UD 0 LEQ 00 ω PUP2 VCC 100 pF

Note: Resistor on pin 3 is required and should be placed as close to the part as possible to avoid package resonance and meet error specifications over frequency.

## Figure 17. Serial Interface Timing Diagram

# Table 7. 5-Bit Attenuator Serial ProgrammingRegister Map

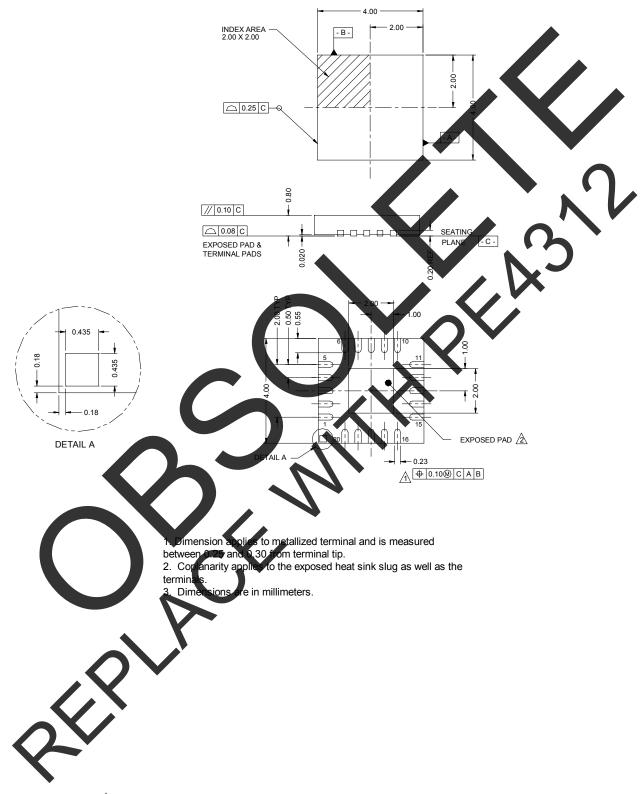

## Figure 19. Package Drawing

Document No. 70-0159-06 | www.psemi.com

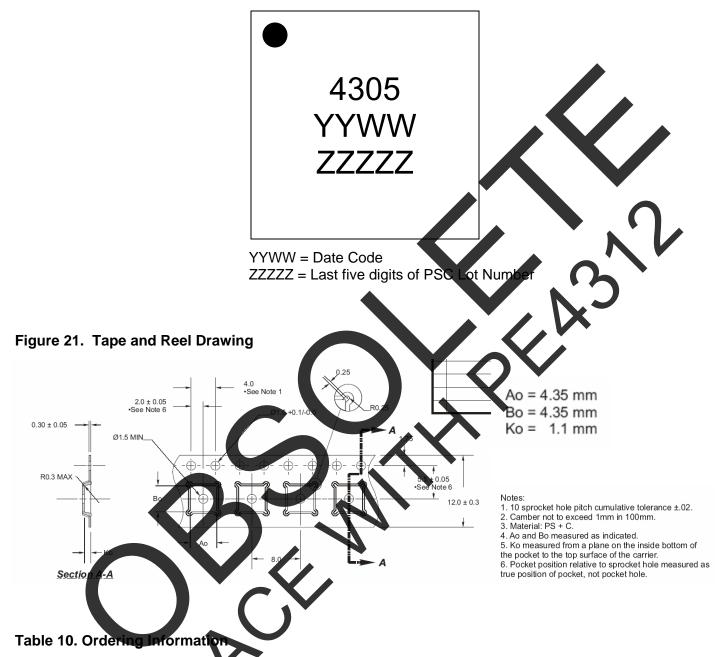

## Figure 20. Marking Specifications

| Order Code | Part Marking | Description               | Package                 | Shipping Method  |  |

|------------|--------------|---------------------------|-------------------------|------------------|--|

| 4305-00    | PE4305-EK    | PE4305-20MLP 4x4mm-EK     | Evaluation Kit          | 1 / Box          |  |

| 4305-51    | 4305         | PE4305G-20MLP 4x4mm-75A   | Green 20-lead 4x4mm QFN | 75 units / Tube  |  |

| 4305-52    | 4305         | PE4305G-20MLP 4x4mm-3000C | Green 20-lead 4x4mm QFN | 3000 units / T&R |  |

$\mathcal{C}^{\vee}$

©2003-2008 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0159-06 | UltraCMOS<sup>™</sup> RFIC Solutions

## **Sales Offices**

#### The Americas

#### **Peregrine Semiconductor Corporation**

9380 Carroll Park Drive San Diego, CA 92121 Tel: 858-731-9400 Fax: 858-731-9499

## Europe

#### Peregrine Semiconductor Europe

Bâtiment Maine 13-15 rue des Quatre Vents F-92380 Garches, France Tel: +33-1-4741-9173 Fax : +33-1-4741-9173

## Space and Defense Products

#### Americas:

Tel: 858-731-9453

#### Europe, Asia Pacific:

180 Rue Jean de Guiramand 13852 Aix-En-Provence Cedex 3, France Tel: +33-4-4239-3361 Fax: +33-4-4239-7227

## Peregrine Semiconductor, Asia Pacific (APAC)

Shanghai, 200040, P.R. China Tel: +86-21-5836-8276 Fax: +86-21-5836-7652

#### Peregrine Semiconductor, Kore

#B-2607, Kolon Tripolis, 210 Geumgok-dong, Bundang-gu, Seongnam-si Gyeonggi-do, 463-942 South Korea Tel: +82-31-728-3939 Fax: +82-31-728-3940

## Peregrine Semiconductor K.K., Japan

Teikoku Hotel Tower 10B-6 1-1-1 Uchisaiwai-cho, Chiyoda-ku Tokyo 100-0011 Japan Tel: +81-3-3502-5211 Fax: +81-3-3502-5213

For a list of representatives in your area, please refer to our Web site at: www.psemi.com

## Data Sheet Identification

## Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and reatures may change in any manner without notice.

## Preliminary Specification

The data sheet contains preliminary data. Additional data may be added at a later date. Peregnine reserves the right to change specifications at any time without notice in order to supply the best possible product.

## Product Specification

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customere of the intervied changes by issuing a DCN (Document Change Notice).

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, and UTSi are registered trademarks and UltraCMOS, HaRP and MultiSwitch are trademarks of Peregrine Semiconductor Corp.

Document No. 70-0159-06 | www.psemi.com