DLPS029E - APRIL 2013-REVISED FEBRUARY 2018

DLPC350

# DLPC350 DLP® Digital Controller for DLP4500 and DLP4500NIR DMDs

#### **Features**

- Required for Reliable Operation of the DLP4500 and DLP4500NIR DMDs

- High Speed Pattern Display Mode

- 1-Bit Binary Pattern Rates to 4225 Hz

- 8-Bit Grayscale Pattern Rates to 120 Hz

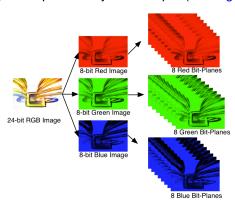

- 1-to-1 Input Mapping to Micromirrors

- Multiple Bit Depths and LEDs in Pattern Sequences

- Easy Synchronization with Cameras and Sensors

- Two Configurable Input Triggers

- Two Configurable Output Triggers

- 14 Fully Programmable GPIO Signals

- 64 Mb Internal RAM

- Stores up to 48 1-Bit Patterns

- No External Volatile Memory Required

- Supports up to 32 MB External Parallel Flash for Increased Pattern Storage

- Multiple Configuration Interfaces

- One USB 1.1 SlavePort

- Two I<sup>2</sup>C Ports

- LED PWM Generators

- Video Display Mode of Operation

- 10- to 120-Hz Full Color Frame Rates

- YUV, YCrCb, or RGB Input Data Formats

- **Integrated Micromirror Drivers**

- Integrated Clock Generation

### Applications

- Machine Vision

- 3D Depth Measurement and Capture

- Robotic Guidance

- Inline Surface Inspection

- Pick and Place

- Spectrometers (Chemical Analysis)

- Process Analyzers

- Laboratory Equipment

- **Dedicated Analyzers**

- 3D Printers

- Medical Instruments

- 3D Dental Scanners

- Vascular Imaging

- Microscopes

- 3D Biometrics

- Fingerprint Recognition

- **Facial Recognition**

- Single-Pixel Cameras

- Laser Marking

# Description

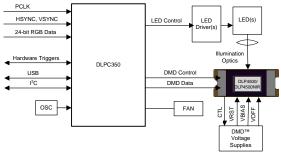

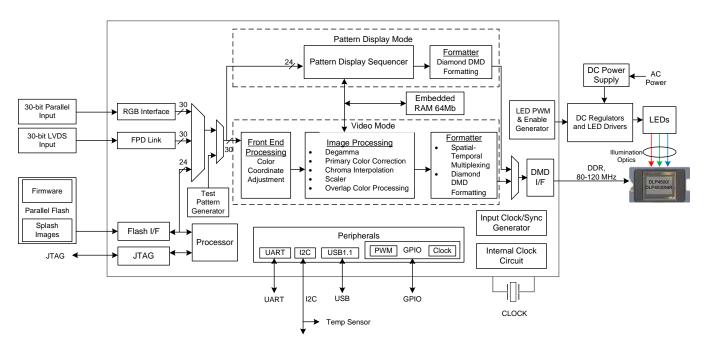

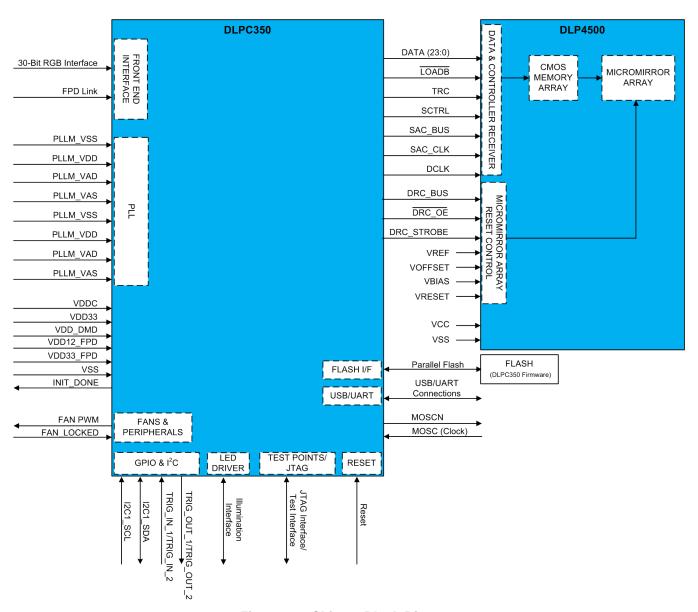

The DLPC350 digital controller is required for reliable operation of the DLP4500 or DLP4500NIR digital micromirror device (DMD). The DLPC350 controller provides a convenient, multi-functional interface between user electronics and the DMD, enabling high-speed pattern rates, along with LED control and data formatting for multiple input formats.

The DLPC350 controller provides input and output trigger signals for synchronizing displayed patterns with a camera, sensor, or other peripherals. The controller enables integration into small-form-factor and low-cost light steering applications. Applications include 3D scanning or metrology systems, spectrometers, interactive displays, chemical analyzers, medical instruments, and other end equipment that requires spatial light modulation (light steering and patterning).

The DLPC350 controller is the data formatting and DMD controlling ASIC for either the visible or nearinfrared (NIR) version of the DLP4500. For further DLPR350 details. please see the firmware homepage, the DLP4500 data sheet, and the DLP4500NIR data sheet.

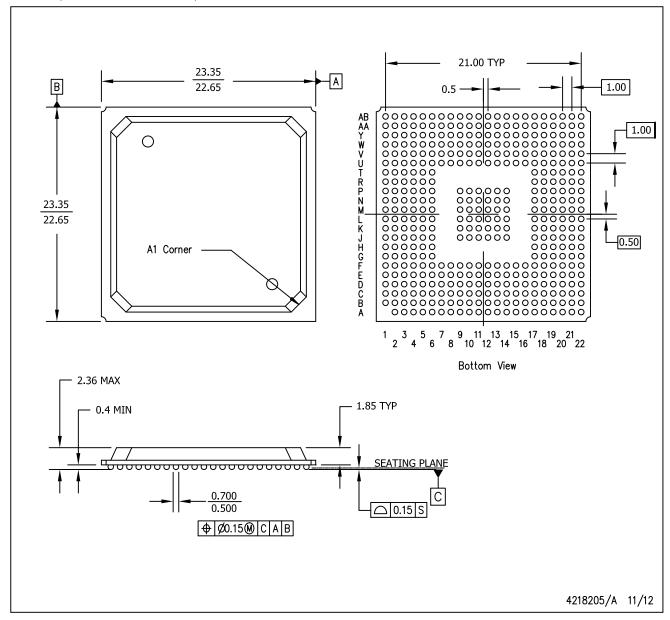

#### Device Information<sup>(1)</sup>

| ORDER NUMBER | PACKAGE   | BODY SIZE         |

|--------------|-----------|-------------------|

| DLPC350      | BGA (419) | 23.4 mm × 23.4 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

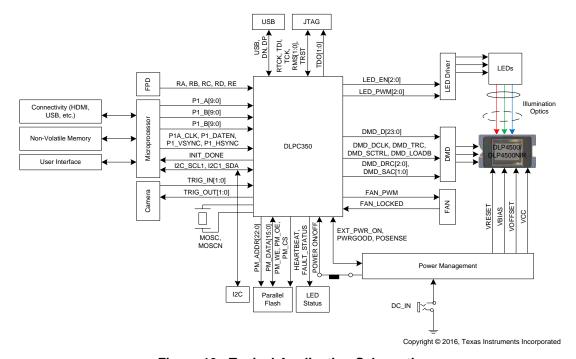

#### Simplified Schematic

Copyright © 2016, Texas Instruments Incorpo

#### **Table of Contents**

| 1 | Features 1                                                                   | 7  | Parameter Measurement Information    | 26 |

|---|------------------------------------------------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                                                               |    | 7.1 Power Consumption                | 26 |

| 3 | Description 1                                                                | 8  | Detailed Description                 | 27 |

| 4 | Revision History2                                                            |    | 8.1 Overview                         |    |

| 5 | Pin Configuration and Functions4                                             |    | 8.2 Functional Block Diagram         | 28 |

| 6 | Specifications                                                               |    | 8.3 Feature Description              | 30 |

| • | 6.1 Absolute Maximum Ratings                                                 |    | 8.4 Device Functional Modes          | 31 |

|   | 6.2 ESD Ratings                                                              | 9  | Application and Implementation       | 35 |

|   | 6.3 Recommended Operating Conditions                                         |    | 9.1 Application Information          | 35 |

|   | 6.4 Thermal Information                                                      |    | 9.2 Typical Applications             | 35 |

|   | 6.5 I/O Electrical Characteristics                                           | 10 | Power Supply Recommendations         | 40 |

|   | 6.6 I <sup>2</sup> C0 and I <sup>2</sup> C1 Interface Timing Requirements 15 |    | 10.1 System Power and Reset          | 40 |

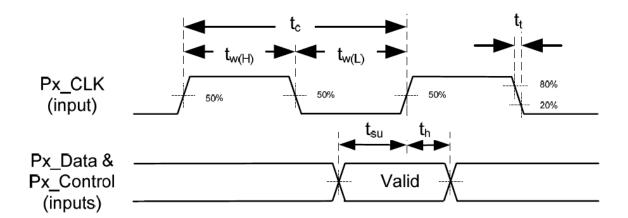

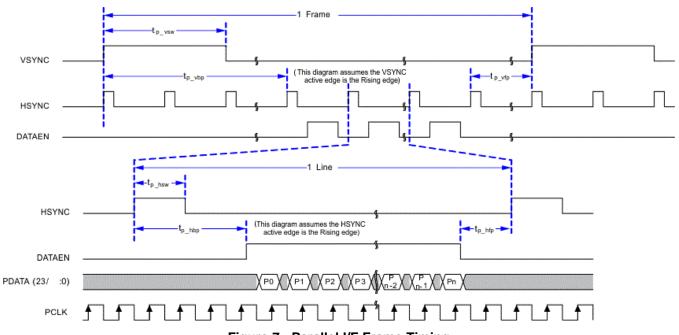

|   | 6.7 Port 1 Input Pixel Interface Timing Requirements 16                      | 11 | Layout                               | 45 |

|   | 6.8 Port 2 Input Pixel Interface (FPD-Link Compatible                        |    | 11.1 Layout Guidelines               | 45 |

|   | LVDS Input) Timing Requirements                                              |    | 11.2 Layout Example                  | 50 |

|   | 6.9 System Oscillator Timing Requirements 16                                 | 12 | Device and Documentation Support     | 55 |

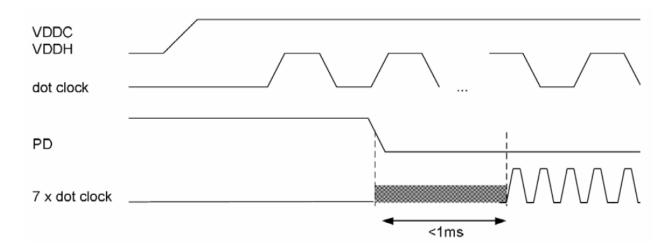

|   | 6.10 Reset Timing Requirements                                               |    | 12.1 Device Support                  |    |

|   | 6.11 Video Timing Input Blanking Specification 20                            |    | 12.2 Documentation Support           |    |

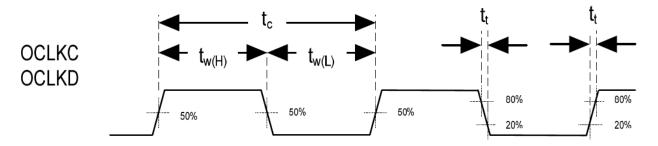

|   | 6.12 Programmable Output Clocks Switching                                    |    | 12.3 Trademarks                      |    |

|   | Characteristics                                                              |    | 12.4 Glossary                        | 56 |

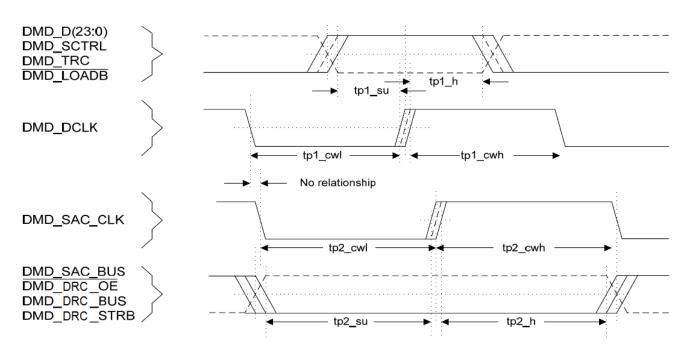

|   | 6.13 DMD Interface Switching Characteristics                                 | 13 | Mechanical, Packaging, and Orderable |    |

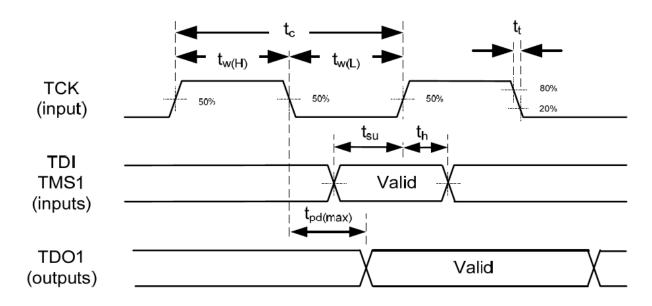

|   | 6.14 JTAG Interface: I/O Boundary Scan Application Switching Characteristics |    | Information                          | 56 |

|   | Switching Characteristics23                                                  |    | 13.1 Package Option Addendum         | 57 |

|   |                                                                              |    |                                      |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision D (August 2016) to Revision E                                                                                                                                                                                  | Page   |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| •  | Corrected LEDx_PWM and LEDx_EN descriptions in <i>Pin Functions</i> table                                                                                                                                                           | 9      |

| •  | Added information about pullup resistor requirements on USB_DAT_P and other USB clarifying notes in <i>Pin Functions</i> table                                                                                                      | 9      |

| •  | Changed FAN_LOCKED pin to indicate it is unimplemented and FAM_PWM pin to indicate it is not user controllable in <i>Pin Functions</i> table                                                                                        |        |

| •  | Corrected DMD interface setup and hold timings to be minimum values and updated the corresponding note                                                                                                                              | 23     |

| •  | Updated "pulse-duration modulation" to "pulse width modulation" in Overview subsection of Detailed Description                                                                                                                      | 27     |

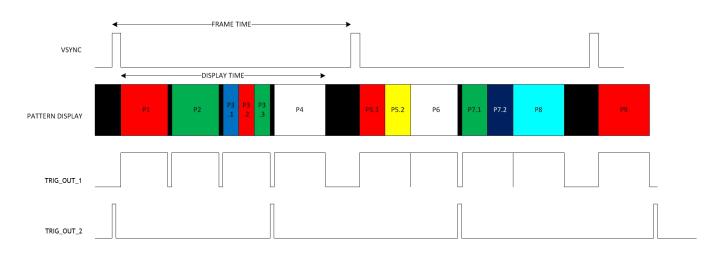

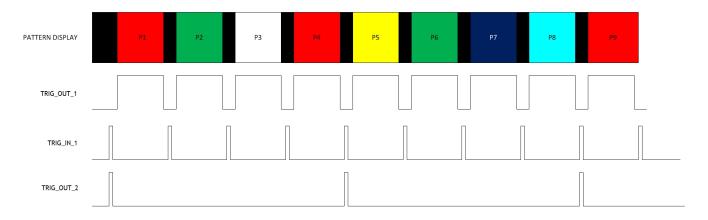

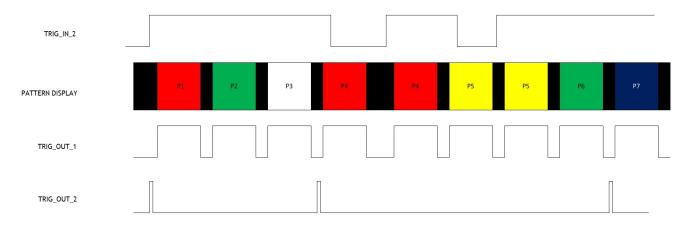

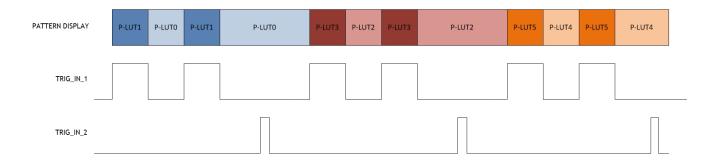

| •  | Updated language concerning structured light applications related to the buffer, trigger modes, and video algorithms; also added additional requirements related to the maximum pattern speed in <i>Structured Light Applicatio</i> | ons 31 |

| •  | Added Table 7, which lists summaries of trigger modes, and updated corresponding descriptions                                                                                                                                       | 31     |

| •  | Added DMD_TRC and DMD_LOADB to Routing Priority table                                                                                                                                                                               | 49     |

| •  | Deleted mention of spread-spectrum clock, which is not supported                                                                                                                                                                    | 53     |

| •  | Added MSL Peak Temp to Packaging Information                                                                                                                                                                                        | 57     |

# Changes from Revision C (September 2013) to Revision D

Changed title of datasheet to DLPC350 DLP Digital Controller for DLP4500 and DLP4500NIR DMDs

Updated "High Speed Pattern Sequence Mode" to "High Speed Pattern Display Mode" in *Features* Corrected internal RAM space to 64 Mb and deleted redundant "Stores up to 48 1-Bit Patterns"

Moved External Parallel Flash up to bullet point; changed 64 MB to 32 MB

Changed "Video Projection Mode" to "Video Display Mode"

Product Folder Links: DLPC350

Page

| •  | Changed several phrases in description                                                                                                                               | 1          |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| •  | Changed "NIR" to "near-infrared (NIR)"                                                                                                                               | 1          |

| •  | Added direct links to DLPR350 firmware and DLP4500 data sheet                                                                                                        | 1          |

| •  | Changed Description field of I2C_ADDR_SEL in Pin Function Descriptions                                                                                               | 5          |

| •  | Changed I2C bus max to reference \( \begin{aligned} \charge CO \) and \( \beta C1 \) Interface Timing Requirements \( (1)(2)(3) \) in Pin Function Description table |            |

| •  | Moved and changed "e.g. HDMI, BT656" in Pin Function Descriptions table                                                                                              | 5          |

| •  | Updated note on ICTSEN and TRST in description column of Pin Function Descriptions table                                                                             |            |

| •  | Removed Machine Model ESD information from ESD Ratings                                                                                                               |            |

| •  | Changed Operating junction temperature to 105°C in Recommended Operating Conditions                                                                                  |            |

| •  | Changed table notes for \$\frac{\cappa CO}{c}\$ and \$\frac{\cappa C1}{c}\$ Interface Timing Requirements \$^{(1)(2)(3)}\$                                           |            |

| •  | Added exception for 120 Hz source in Source Input Blanking                                                                                                           |            |

| •  | Added VSYNC and HSYNC high value to Table 3                                                                                                                          |            |

| •  | Added Table 4                                                                                                                                                        | 20         |

| •  | Added Figure 7                                                                                                                                                       |            |

| •  | Added clarification on putting DLPC350 in tri-state during JTAG boundary scan in Board Level Test Support                                                            | 30         |

| •  | Changed 48 bit-plane" to "48 1-bit planes                                                                                                                            |            |

| •  | Clarified wording about mapping options in (LVDS) Receiver Supported Pixel Mapping Modes                                                                             |            |

| •  | Added Link to DLPR350 firmware page                                                                                                                                  |            |

| •  | Corrected flash access read and write timing to fixed values                                                                                                         |            |

| •  | Removed subsection Application Performance Plot and figure                                                                                                           |            |

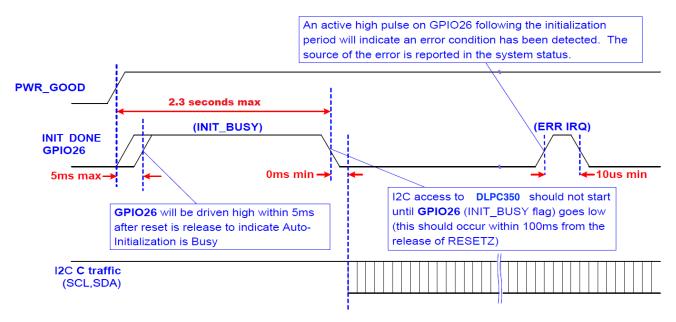

| •  | Changed Figure 23 to reference DLPC350 and INIT_BUSY timing to 2.3 s max                                                                                             | 44         |

| •  | Added DLPC350 Configuration and Support Firmware (DLPR350) in Related Documentation                                                                                  | <u>5</u> 6 |

| _  | hanges from Revision B (September 2013) to Revision C                                                                                                                | Page       |

| •  | Updated to new TI standards and rearranged content for the new data sheet flow                                                                                       |            |

| •  |                                                                                                                                                                      |            |

| •  | Moved the pin descriptions as part of new data sheet flow                                                                                                            |            |

| •  | Removed empty Conditions column from Absolute Maximum Ratings.                                                                                                       |            |

| •  | Separated the handling ratings from the absolute maximum ratings                                                                                                     |            |

| •  | Removed empty Conditions column from the <i>Recommended Operating Conditions</i> table                                                                               | 13<br>55   |

| _  | Added Device and Documentation Support section                                                                                                                       | 33         |

| CI | hanges from Revision A (May 2013) to Revision B                                                                                                                      | Page       |

| •  | Added PIB_CLK and P1C_CLK to Pin Function Descriptions                                                                                                               | 5          |

| •  | Deleted PM_CS_0 from FLASH INTERFACE in Pin Function Descriptions                                                                                                    | 8          |

| •  | Deleted Y16 and AB17 from the RESERVED PINS list in Pin Function Descriptions                                                                                        | 10         |

| •  | Added PM_CS_0 to the RESERVED PINS LIST in Pin Function Descriptions                                                                                                 | 10         |

| •  | Deleted "PM_CS_0 - available for optional Flash device ( ≤ 128 Mb)" From the Program Memory Flash Interface section                                                  | 38         |

|    | hanges from Original (April 2013) to Revision A                                                                                                                      | Page       |

| U  | nangos nom ongina (Apin 2015) to Nevision A                                                                                                                          | raye       |

|    | Changed the device From: Preview To: Production                                                                                                                      | 1          |

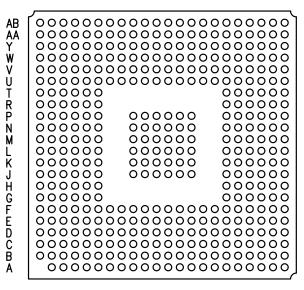

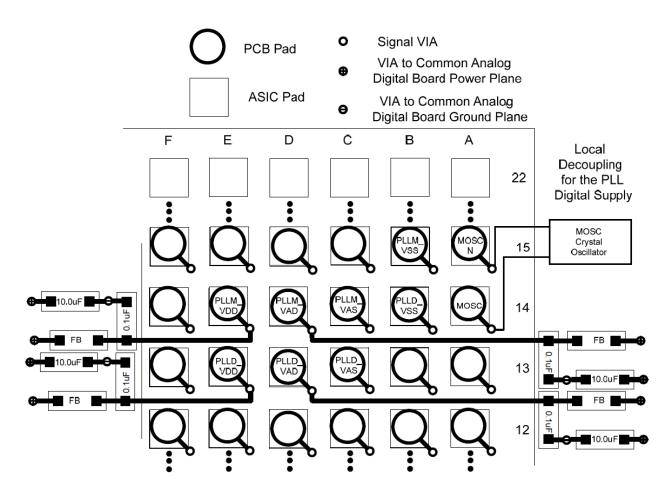

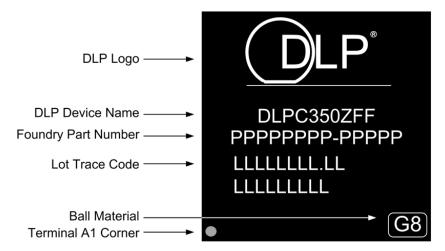

# 5 Pin Configuration and Functions

ZFF Package 419 Pins BGA Bottom View

#### 1 3 5 7 9 11 13 15 17 19 21 2 4 6 8 10 12 14 16 18 20 22

#### Pin Functions

| FIII FUIICUOIIS    |        |           |                     |                      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------|--------|-----------|---------------------|----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN <sup>(1)</sup> |        | 1/0       | I/O                 |                      | CLK    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| NAME               | NUMBER | DOWED IYP | TYPE                | INTERNAL TERMINATION | SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CONTROL            |        |           |                     |                      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

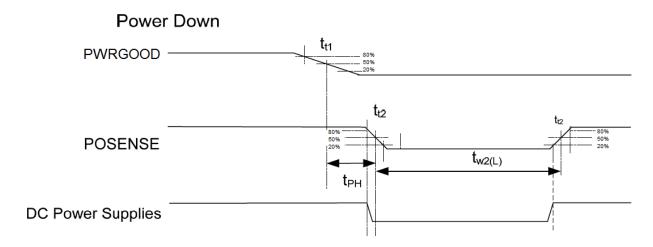

| PWRGOOD            | H19    | VDDC      | I <sub>4</sub><br>H |                      | Async  | PWRGOOD is an active high signal with hysteresis that is generated by an external power supply or voltage monitor. A high value indicates all power is within operating voltage specs and the system is safe to exit its reset state. A transition from high to low should indicate that the controller or DMD supply voltage will drop below their rated minimum level within the next 0.5 ms (POSENSE must remain active high during this interval). This is an early warning of an imminent power loss condition. This warning is required to enhance long-term DMD reliability. A DMD park sequence, followed by a full controller reset, is performed by the DLPC350 controller when PWRGOOD goes low for a minimum of 4 µs protecting the DMD. This minimum de-assertion time is used to protect the input from glitches. Following this, the DLPC350 controller is held in its reset state as long as PWRGOOD is low. PWRGOOD must be driven high for normal operation. The DLPC350 controller acknowledges PWRGOOD as active after it is driven high for a minimum of 625 ns. Utilizes hysteresis. |  |

| POSENSE            | G21    |           | I <sub>4</sub><br>H |                      | Async  | Power-On Sense is an active high input signal with hysteresis that is generated by an external voltage monitor circuit. POSENSE must be driven inactive (low) when any of the controller supply voltages are below minimum operating voltage specs. POSENSE must be active (high) when all controller supply voltages remain above minimum specs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| POWER_ON_OFF       | N21    | VDD33     | B <sub>2</sub>      |                      | Async  | POWER_ON_OFF is an active high input signal which controls the DLPC350 standby feature. When this signal is externally driven high, the DLPC350 is commanded to active mode. When driven low, the DLPC350 is commanded to standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

<sup>(1)</sup> See General Handling Guidelines for Unused CMOS-Type Pins in the Layout section for instructions on handling unused pins.

<sup>(2)</sup> I/O Type: I indicates input, O indicates output, B indicates bidirectional, and H indicates hysteresis. See Table 2 for subscript explanation.

| PIN <sup>(1)</sup> |            | 1/0         | I/O                     |                                                                                                                            | CLK      |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|------------|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NUMBER     | POWER       | TYPE                    | INTERNAL TERMINATION                                                                                                       | SYSTEM   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                            |

| EXT_PWR_ON         | D21        | VDD33       | B <sub>2</sub>          |                                                                                                                            | Async    | Signal to host processor or power supply to indicate that the DLPC350 controller is powered on. Asserted just before INIT_DONE.                                                                                                                                                                                                                                                                                        |

| HOLD_IN_BOOT       | D18        | VDD33       | B <sub>2</sub>          | External pullup required                                                                                                   | N/A      |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INIT_DONE          | F19        | VDD33       | B <sub>2</sub>          |                                                                                                                            | Async    | Prior to transferring part of code from parallel flash content to internal memory, the internal memory is initialized and a memory test is performed. The result of this test (pass or fail) is recorded in the system status. If the memory test fails, the initialization process is halted. INIT_DONE is asserted twice to indicate an error situation. See Figure 23 and note that GPIO26 is the INIT_DONE signal. |

| I2C_ADDR_SEL       | F21        | VDD33       | B <sub>2</sub>          |                                                                                                                            | Async    | This signal is sampled during power-up. If the signal is low, the I <sup>2</sup> C slave addresses are 0x34 and 0x35. If the signal is high, the I <sup>2</sup> C slave addresses are 0x3A and 0x3B. After the system has been initialized, this signal is available as a GPIO.                                                                                                                                        |

| I2C1_SCL           | J3         | VDD33       | B <sub>2</sub>          | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 $k\Omega.$                                  | N/A      | l <sup>2</sup> C clock. bidirectional, open-drain signal. l <sup>2</sup> C slave clock input from the external processor. This bus supports the frequency as specified in ${}^{\rho}CO$ and ${}^{\rho}C1$ Interface Timing Requirements (3)(4)(5).                                                                                                                                                                     |

| I2C1_SDA           | J4         | VDD33       | B <sub>2</sub>          | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 $k\Omega.$                                  | I2C1_SCL | l <sup>2</sup> C data. bidirectional, open drain signal. l <sup>2</sup> C slave to accept command or transfer data to and from the external processor. This bus supports the frequency as specified in <i>PCO</i> and <i>PC1</i> Interface Timing Requirements <sup>(3)</sup> (4)(5).                                                                                                                                  |

| I2C0_SCL           | M2         | VDD33       | B <sub>8</sub>          | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 $k\Omega$ . This input is not 5-V tolerant. | N/A      | I <sup>2</sup> C Bus 0, Clock; I <sup>2</sup> C master for on-board peripherals such as temperature sensor. This bus supports the frequency as specified in $^{\rho}CO$ and $^{\rho}C1$ Interface Timing Requirements $^{(3)}$ (4) (5).                                                                                                                                                                                |

| I2C0_SDA           | М3         | VDD33       | В <sub>8</sub>          | Requires an external pullup to 3.3 V. The minimum acceptable pullup value is 1 $k\Omega$ . This input is not 5-V tolerant. | 12C0_SCL | $I^2C$ Bus 0, Data; $I^2C$ master for on-board peripherals such as temperature sensor. This bus supports the frequency as specified in ${}^{\rho}CO$ and ${}^{\rho}C1$ Interface Timing Requirements ${}^{(3)}(4)^{(5)}$ .                                                                                                                                                                                             |

| SYSTEM CLOCK       |            |             |                         |                                                                                                                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                        |

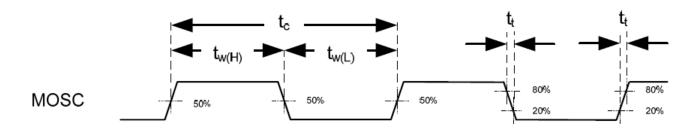

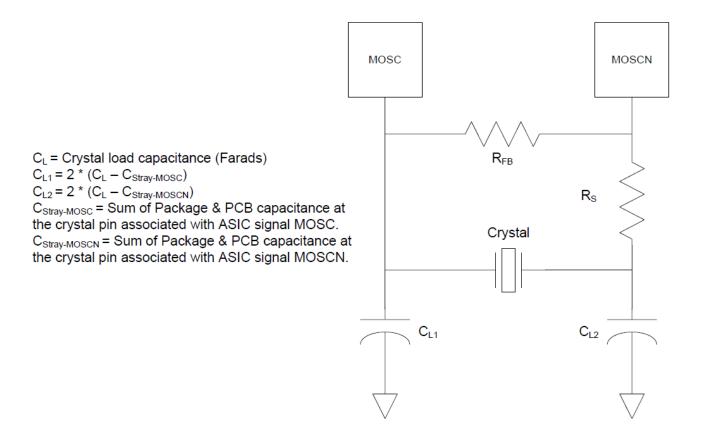

| MOSC               | A14        | VDD33       | I <sub>10</sub>         |                                                                                                                            | N/A      | System clock oscillator input (3.3-V LVCMOS). Note that the MOSC must be stable a maximum of 25 ms after POSENSE transitions from high to low.                                                                                                                                                                                                                                                                         |

| MOSCN              | A15        | VDD33       | O <sub>10</sub>         |                                                                                                                            | N/A      | MOSC crystal return                                                                                                                                                                                                                                                                                                                                                                                                    |

| PORT 1: PARALLE    | L VIDEO/GR | APHICS INPU | T <sup>(6)</sup> (7) (8 | 9)                                                                                                                         |          |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P1A_CLK            | W15        | VDD33       | l <sub>4</sub>          | Includes an internal pulldown                                                                                              | N/A      | Port 1 input data pixel write clock 'A'                                                                                                                                                                                                                                                                                                                                                                                |

| P1B_CLK            | AB17       | VDD33       | I <sub>4</sub>          | Includes an internal pulldown                                                                                              | N/A      | Port 1 input data pixel write clock 'B'                                                                                                                                                                                                                                                                                                                                                                                |

| P1C_CLK            | Y16        | VDD33       | I <sub>4</sub>          | Includes an internal pulldown                                                                                              | N/A      | Port 1 input data pixel write clock 'C'                                                                                                                                                                                                                                                                                                                                                                                |

| P1_VSYNC           | Y15        | VDD33       | B₁<br>H                 | Includes an internal pulldown                                                                                              | P1A_CLK  | Port 1 vertical sync; utilizes hysteresis                                                                                                                                                                                                                                                                                                                                                                              |

| P1_HSYNC           | AB16       | VDD33       | B₁<br>H                 | Includes an internal pulldown                                                                                              | P1A_CLK  | Port 1 horizontal sync; utilizes hysteresis                                                                                                                                                                                                                                                                                                                                                                            |

- (3) Meets I<sup>2</sup>C timing per the I<sup>2</sup>C Bus Specification, unless otherwise noted. For reference see version 2.1 of the Phillips/NXP specification.

- (4) The maximum clock frequency does not account for rise time, nor added capacitance of PCB or external components which may adversely impact this value.

- (5) By definition, I<sup>2</sup>C transactions will operate at the speed of the slowest device on the bus and thus there is no requirement to match the speed grade of all devices in the system. However if Full-speed operation is desired, it will be necessary to ensure the other I<sup>2</sup>C devices support full-speed operation as well. In addition to other devices slowing down bus operation, the length of the line (due to its capacitance) and the value of the I<sup>2</sup>C pullup resistors will also influence the max achievable speed.

- (6) Port 1 can be used to support multiple source options (e.g. HDMI, BT656) for a given product. To do so, the data bus from both source components must be connected to the same port 1 pins and control given to the DLPC350 to 3-state the "inactive" source. Tying them together like this will cause some signal degradation due to reflections on the 3-stated path.

- (7) The A, B, and C input data channels of Port 1 can be internally swapped for optimum board layout.

- (8) Sources feeding less than the full 10-bits per color component channel should be MSB justified when connected to the DLPC350 and LSBs tied off to zero. For example, an 8-bit per color input should be connected to bits 9:2 of the corresponding A, B, or C input channel. BT656 are 8 or 10 bits in width. If a BT656 type input is utilized, the data bits must be MSB justified as with the other types of input sources on either of the A, B, or C data input channels.

|                    | Pin Functions (continued) |               |                |                                 |         |                                                                               |  |

|--------------------|---------------------------|---------------|----------------|---------------------------------|---------|-------------------------------------------------------------------------------|--|

| PIN <sup>(1)</sup> | ı                         | 1/0           | I/O            | INTERNAL TERMINATION            | CLK     | DESCRIPTION                                                                   |  |

| NAME               | NUMBER                    | POWER         | TYPE           | INTERNAL TERMINATION            | SYSTEM  | DESCRIPTION                                                                   |  |

| P1_DATEN           | AA16                      | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 data enable                                                            |  |

| P1_FIELD           | W14                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 field sync; required for interlaced sources only (and not progressive) |  |

| P1_A_9             | AB20                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 128)                            |  |

| P1_A_8             | AA19                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 64)                             |  |

| P1_A_7             | Y18                       | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 32)                             |  |

| P1_A_6             | W17                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 16)                             |  |

| P1_A_5             | AB19                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 8)                              |  |

| P1_A_4             | AA18                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 4)                              |  |

| P1_A_3             | Y17                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 2)                              |  |

| P1_A_2             | AB18                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 1)                              |  |

| P1_A_1             | W16                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 0.5)                            |  |

| P1_A_0             | AA17                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 A channel input pixel data (bit weight 0.25)                           |  |

| P1_B_9             | U21                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 128)                            |  |

| P1_B_8             | U20                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 64)                             |  |

| P1_B_7             | V22                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 32)                             |  |

| P1_B_6             | U19                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 16)                             |  |

| P1_B_5             | V21                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 8)                              |  |

| P1_B_4             | W22                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 4)                              |  |

| P1_B_3             | W21                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 2)                              |  |

| P1_B_2             | AA20                      | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 1)                              |  |

| P1_B_1             | Y19                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 0.5)                            |  |

| P1_B_0             | W18                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 B channel input pixel data (bit weight 0.25)                           |  |

| P1_C_9             | P21                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 128)                            |  |

| P1_C_8             | P22                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 64)                             |  |

| P1_C_7             | R19                       | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 32)                             |  |

| P1_C_6             | R20                       | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 16)                             |  |

| P1_C_5             | R21                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 8)                              |  |

| P1_C_4             | R22                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 4)                              |  |

| P1_C_3             | T21                       | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 2)                              |  |

| P1_C_2             | T20                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 1)                              |  |

| P1_C_1             | T19                       | VDD33         | $I_4$          | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 0.5)                            |  |

| P1_C_0             | U22                       | VDD33         | l <sub>4</sub> | Includes an internal pulldown   | P1A_CLK | Port 1 C channel input pixel data (bit weight 0.25)                           |  |

| PORT 2: FPD-LINK   | COMPATIBI                 |               | APHICS         | INPUT <sup>(9)</sup>            |         |                                                                               |  |

| RCK_IN_P           | Y9                        | VDD33_FP<br>D | l <sub>5</sub> | Includes weak internal pulldown | N/A     | Positive differential input signal for Clock, FPD-Link receiver               |  |

| RCK_IN_N           | W9                        | VDD33_FP<br>D | l <sub>5</sub> | Includes weak internal pulldown | N/A     | Negative differential input signal for Clock, FPD-Link receiver               |  |

| RA_IN_P            | AB10                      | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown | RCK_IN  | Positive differential input signal for data channel A, FPD-<br>Link receiver  |  |

| RA_IN_N            | AA10                      | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown | RCK_IN  | Negative differential input signal for data channel A, FPD-Link receiver      |  |

| RB_IN_P            | Y11                       | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown | RCK_IN  | Positive differential input signal for data channel B, FPD-<br>Link receiver  |  |

| RB_IN_N            | W11                       | VDD33_FP<br>D | l <sub>5</sub> | Includes weak internal pulldown | RCK_IN  | Negative differential input signal for data channel B, FPD-Link receiver      |  |

| RC_IN_P            | AB12                      | VDD33_FP<br>D | l <sub>5</sub> | Includes weak internal pulldown | RCK_IN  | Positive differential input signal for data channel C, FPD-Link receiver      |  |

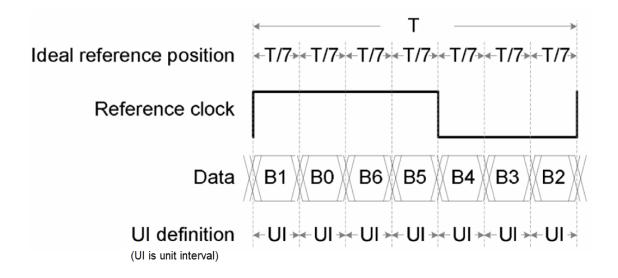

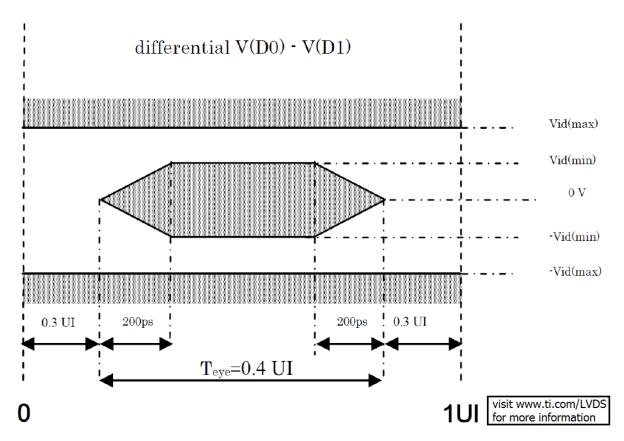

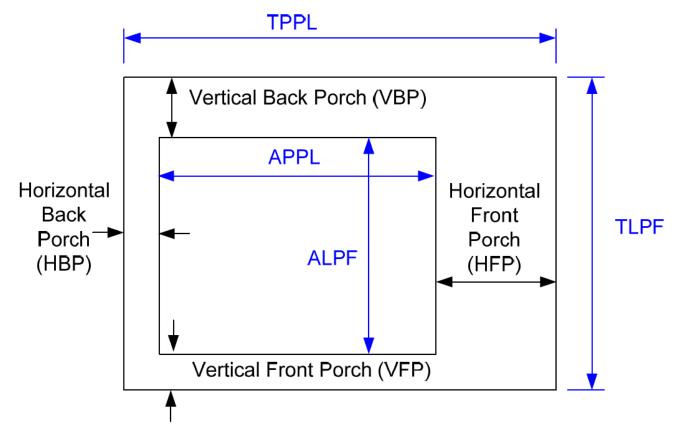

<sup>(9)</sup> Port 2 is a single-channel FPD-Link compatible input interface. FPD-Link is a defacto industry standard flat-panel display interface, which utilizes the high bandwidth capabilities of LVDS signaling to serialize video or graphics data down to a couple wires to provide a low wire count and low EMI interface. Port 2 supports sources rates up to a maximum effective clock of 90 MHz. The Port 2 input pixel data must adhere to one of four supported data mapping formats (see Table 9). Given that Port 2 inputs contain weak pulldown resistors, they can be left floating when not used.

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

| PIN <sup>(1)</sup> |        | I/O           | I/O            |                                                             | CLK               |                                                                                                                            |

|--------------------|--------|---------------|----------------|-------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| NAME               | NUMBER | POWER         | TYPE           | INTERNAL TERMINATION                                        | SYSTEM            | DESCRIPTION                                                                                                                |

| RC_IN_N            | AA12   | VDD33_FP<br>D | l <sub>5</sub> | Includes weak internal pulldown                             | RCK_IN            | Negative differential input signal for data channel C, FPD-Link receiver                                                   |

| RD_IN_P            | Y13    | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown                             | RCK_IN            | Positive differential input signal for data channel D, FPD-<br>Link receiver                                               |

| RD_IN_N            | W13    | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown                             | RCK_IN            | Negative differential input signal for data channel D, FPD-Link receiver                                                   |

| RE_IN_P            | AB14   | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown                             | RCK_IN            | Positive differential input signal for data channel E, FPD-<br>Link receiver                                               |

| RE_IN_N            | AA14   | VDD33_FP<br>D | I <sub>5</sub> | Includes weak internal pulldown                             | RCK_IN            | Negative differential input signal for data channel E, FPD-Link receiver                                                   |

| DMD INTERFACE      |        |               |                |                                                             |                   |                                                                                                                            |

| DMD_D0             | A8     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D1             | B8     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D2             | C8     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D3             | D8     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D4             | B11    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D5             | C11    |               |                |                                                             |                   |                                                                                                                            |

| DMD D6             | D11    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D7             | E11    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D8             | C7     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D9             | B10    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D10            | E7     |               |                |                                                             |                   | DMD data sina DMD data sina ana daukla data sata                                                                           |

| DMD D11            | D10    |               |                |                                                             |                   | DMD data pins. DMD data pins are double data rate (DDR) signals that are clocked on both edges of                          |

| DMD_D12            | A6     | VDD_DMD       | O <sub>7</sub> |                                                             | DMD_DCLK          | DMD_DCLK.                                                                                                                  |

| DMD_D13            | A12    |               |                |                                                             |                   | All 24 DMD data signals are use to interface to the DMD.                                                                   |

| DMD_D14            | B12    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D15            | C12    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D16            | D12    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D16            | B7     |               |                |                                                             |                   |                                                                                                                            |

|                    | A10    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D18            | D7     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D19            |        |               |                |                                                             |                   |                                                                                                                            |

| DMD_D20            | B6     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D21            | E9     |               |                |                                                             |                   |                                                                                                                            |

| DMD_D22            | C10    |               |                |                                                             |                   |                                                                                                                            |

| DMD_D23            | C6     |               | _              |                                                             |                   |                                                                                                                            |

| DMD_DCLK           | A9     | VDD_DMD       | O <sub>7</sub> |                                                             | N/A               | DMD data clock (DDR)                                                                                                       |

| DMD_LOADB          | B9     | VDD_DMD       | O <sub>7</sub> |                                                             | DMD_DCLK          | DMD data load signal (active-low)                                                                                          |

| DMD_SCTRL          | C9     | VDD_DMD       | O <sub>7</sub> |                                                             | DMD_DCLK          | DMD data serial control signal                                                                                             |

| DMD_TRC            | D9     | VDD_DMD       | O <sub>7</sub> |                                                             | DMD_DCLK DMD_SAC_ | DMD data toggle rate control                                                                                               |

| DMD_DRC_BUS        | D5     | VDD_DMD       | O <sub>7</sub> |                                                             | CLK               | DMD reset control bus data                                                                                                 |

| DMD_DRC_STRB       | C5     | VDD_DMD       | O <sub>7</sub> |                                                             | DMD_SAC_<br>CLK   | DMD reset control bus strobe                                                                                               |

| DMD_DRC_OE         | B5     | VDD_DMD       | O <sub>7</sub> | Requires a 30 to 51-kΩ external pullup resistor to VDD_DMD. | Async             | DMD reset control enable (active-low)                                                                                      |

| DMD_SAC_BUS        | D6     | VDD_DMD       | 07             |                                                             | DMD_SAC_<br>CLK   | DMD stepped-address control bus data                                                                                       |

| DMD_SAC_CLK        | A5     | VDD_DMD       | O <sub>7</sub> |                                                             | N/A               | DMD stepped-address control bus clock                                                                                      |

| DMD_PWR_EN         | G20    | VDD_DMD       | O <sub>2</sub> |                                                             | Async             | DMD Power Enable control. This signal indicates to an external regulator that the DMD is powered.                          |

| EXRES              | А3     |               | 0              |                                                             | Async             | DMD drive strength adjustment precision reference. A $\pm$ 1% external precision resistor should be connected to this pin. |

| FLASH INTERFACE PM_CS_1 | NUMBER | I/O<br>POWER | TYPE           | INTERNAL TERMINATION   | CLK       | DECOF::-:                                                                                                                  |

|-------------------------|--------|--------------|----------------|------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| PM_CS_1                 |        |              | (2)            | INTERNOLE PERMITORITOR | SYSTEM    | DESCRIPTION                                                                                                                |

| PM_CS_1                 |        |              |                |                        |           |                                                                                                                            |

|                         | U2     | VDD33        | O <sub>2</sub> |                        | Async     | Boot flash (active low). Required for boot memory                                                                          |

| PM_CS_2                 | U1     | VDD33        | O <sub>2</sub> |                        | Async     | Optional for additional flash (up to 128 Mb)                                                                               |

| PM_ADDR_22              | V3     |              |                |                        | ,         | Cp. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10                                                                                 |

| PM_ADDR_21              | W1     |              | B <sub>2</sub> |                        |           |                                                                                                                            |

| PM_ADDR_20              | W2     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_19              | Y1     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_18              | AB2    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_17              | AA3    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_16              | Y4     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_15              | W5     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_14              | AB3    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_13              | AA4    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_12              | Y5     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_11              | W6     | VDD33        |                |                        | Async     | Flash memory address bit                                                                                                   |

| PM_ADDR_10              | AB4    |              | O <sub>2</sub> |                        | ,         | ·                                                                                                                          |

| PM_ADDR_9               | AA5    |              | _              |                        |           |                                                                                                                            |

| PM_ADDR_8               | Y6     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_7               | W7     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_6               | AB5    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_5               | AA6    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_4               | Y7     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_3               | AB6    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_2               | W8     |              |                |                        |           |                                                                                                                            |

| PM_ADDR_1               | AA7    |              |                |                        |           |                                                                                                                            |

| PM_ADDR_0               | AB7    |              |                |                        |           |                                                                                                                            |

| PM_WE                   | V2     | VDD33        | O <sub>2</sub> |                        | Async     | Write enable (active low)                                                                                                  |

| PM_OE                   | U4     | VDD33        | O <sub>2</sub> |                        | Async     | Output enable (active low)                                                                                                 |

| PM_BLS_1                | AA8    | VDD33        | O <sub>2</sub> |                        | Async     | Upper byte(15:8) enable                                                                                                    |

| PM_BLS_0                | AB8    | VDD33        | O <sub>2</sub> |                        | Async     | Lower byte(7:0) enable                                                                                                     |

| PM_DATA_15              | M1     |              |                |                        |           |                                                                                                                            |

| PM_DATA_14              | N1     |              |                |                        |           |                                                                                                                            |

| PM_DATA_13              | N2     |              |                |                        |           |                                                                                                                            |

| PM_DATA_12              | N3     | VDDaa        | D              |                        | A 0.110.0 | Data hita unnar huta                                                                                                       |

| PM_DATA_11              | N4     | VDD33        | B <sub>2</sub> |                        | Async     | Data bits, upper byte                                                                                                      |

| PM_DATA_10              | P1     |              |                |                        |           |                                                                                                                            |

| PM_DATA_9               | P2     |              |                |                        |           |                                                                                                                            |

| PM_DATA_8               | P3     |              |                |                        |           |                                                                                                                            |

| PM_DATA_7               | P4     | ·            |                |                        |           |                                                                                                                            |

| PM_DATA_6               | R2     |              |                |                        |           |                                                                                                                            |

| PM_DATA_5               | R3     |              |                |                        |           |                                                                                                                            |

| PM_DATA_4               | R4     | VDDaa        | D              |                        | Async     | Data hita Jawar huta                                                                                                       |

| PM_DATA_3               | T1     | VDD33        | B <sub>2</sub> |                        | Async     | Data bits, lower byte                                                                                                      |

| PM_DATA_2               | T2     |              |                |                        |           |                                                                                                                            |

| PM_DATA_1               | Т3     |              |                |                        |           |                                                                                                                            |

| PM_DATA_0               | T4     |              |                |                        |           |                                                                                                                            |

| LED DRIVER INTERI       | FACE   |              |                |                        |           |                                                                                                                            |

| HEARTBEAT               | C16    | VDD33        | B <sub>2</sub> |                        | Async     | LED blinks continuously (heartbeat) to indicate the system is operational. The period is one second with a 50% duty cycle. |

| FAULT_STATUS            | B16    | VDD33        | B <sub>2</sub> |                        | Async     | LED off indicates any system fault                                                                                         |

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

| PIN <sup>(1</sup> | )      | 1/0          | I/O            | i iii i diictions (co | •             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|--------|--------------|----------------|-----------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NUMBER | I/O<br>POWER | TYPE           | INTERNAL TERMINATION  | CLK<br>SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LEDR_PWM          | K2     |              |                |                       |               | LED red PWM output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |